您好!

EVM 在附加的文件设置下工作正常、但客户电路板的 PLL 锁定不稳定、输出频率略高(所有5个原型 PCB 都相同)。

e2e.ti.com/.../LMK03000_2D8A9A5BAD30E330D730C130E330_.xlsx

我监控了多路复用器的 R 和 N 分频器/2输出、以调查原因。

R divider /2输出正常、但 N divider /2具有稍高的频率(由于 N-div = 3.84MHz、MUX out 最初为1.92MHz、但输出为2.08MHz)。

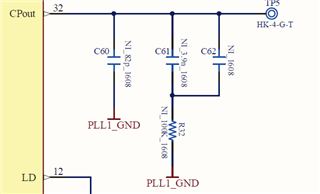

我认为 VCO 的输入电平很低、要求通过寄存器设置提高 CP 电流、但它已经是最大值、因此我无法解决。

电源是一个外部稳压电源(与 EVM 相同的电源)。

出什么问题了? 您是否有任何改进建议?

R 分频器正常、因此至少我认为中的 REF 正常。

这是否是 PCB 布局的问题?

此致、

Hiroshi