大家好、在最近的调试过程中、LMK04806的0延迟模式存在一些问题。 希望原厂能有所帮助。 具体问题如下

e2e.ti.com/.../single-PLL-0_2D00_delay-20211012.txt

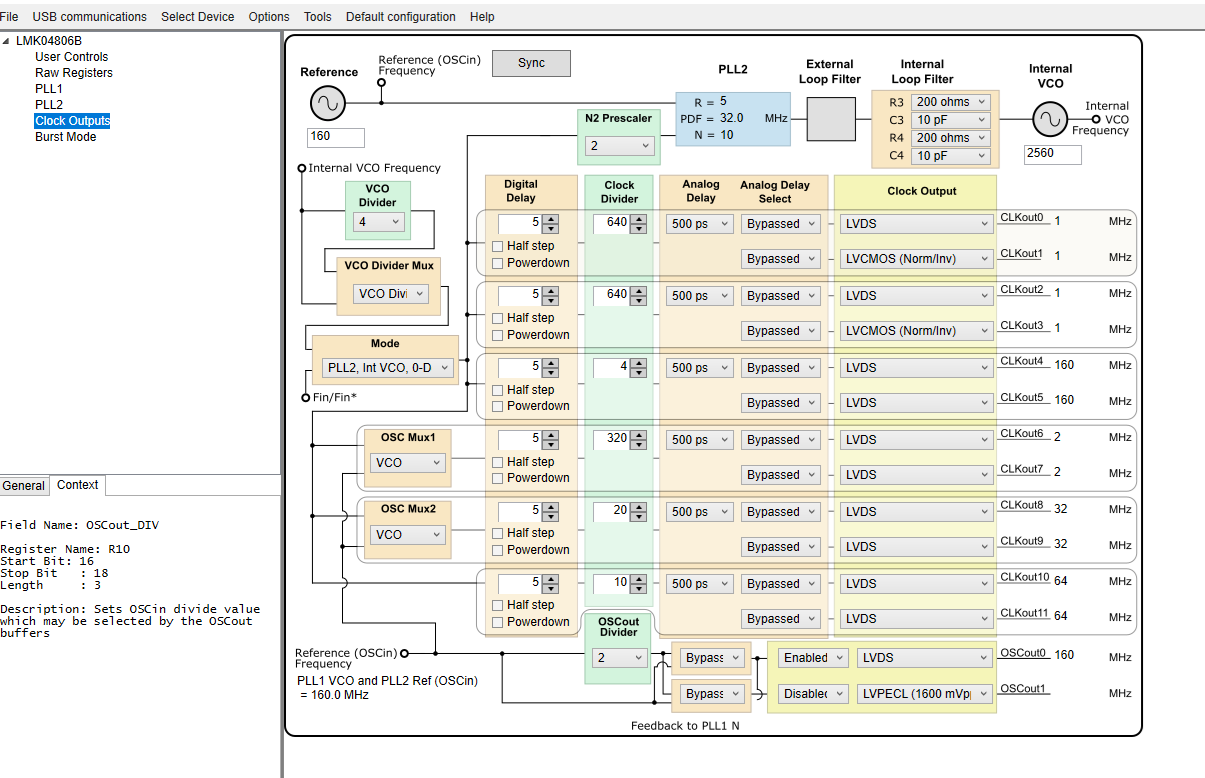

1、在非0延时模式下、如果使用单个 PLL2、时钟输出将根据调整后的设计值正常工作、硬件电路应该可以正常工作、但是在0延时模式下、没有时钟输出、 寄存器设置的接口(请参阅附件中的寄存器表)如下所示

我们的评估应该是寄存器设置或同步信号状态(始终为高电平)错误、导致时钟没有输出、制造商是否可以帮助检查?或者给出使用单 PLL2 0延迟模式的寄存器设置示例?