编号:CS0695848

简短描述:频率偏移问题

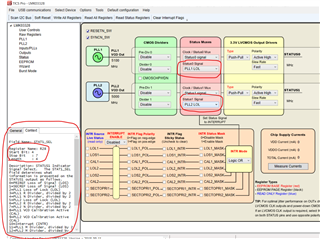

我在 LMK03328RHST 设计中使用 LMK03328RHST、其中 LMK03328RHST 的主输入和辅助输入均为10MHz。 LMK03328RHST 使用 PLL1和 PLL2生成输出时钟。 使用 STATUS0和 STATUS1引脚(分别为1和2)观察 PLL 频率、我已经设置了以下寄存器:

R23 STATUS_MUTE 更改为0x00

R30 PWDN 至0x0A (输出2/3和5断电、同时启用包括 CMOSCHPWDN 在内的其他输出)

R45 CMOSDIVCTL 至0x54 (PLL2CMOSPREDIV = 01b (4)、PLL1CMOSPREDIV = 01b (4)、STATUS1MUX = 01b、STATUS0MUX= 00b)

R46 CMOSDIV0至0x0B (11映射到 PLL1的分频器设置12)

R47 CMOSDIV1至0x09 (9、映射到 PLL2的分频器设置10)

PLL1配置为4800MHz、在预分频器上除以4、在分频器上除以12会在 STATUS0输出上产生100MHz 的输出时钟

PLL2配置为5000MHz、在预分频器上除以4、在分频器上除以10会在 STATUS1输出上产生125MHz 的输出时钟

大约一半的电路上电时间、在 STATUS0和 STATUS1输出上观察到预期频率。 但是、在上电的其他时间、所需的频率在短时间内出现、然后3.3V 显示在 STAUTS0和 STATUS1输出上。 当 STATUS0和 STATUS1输出为3.3V 时、OUT0、OUT4、OUT6和 OUT7输出在编程频率下大约关闭5%。 OUT1、OUT2、OUT3和 OUT5通过寄存器设置禁用、并且没有所需的输出。 例如、当 STATUS0和 STATUS1输出为3.3V 时、OUT6上通常在100MHz 下测量的输出频率使用示波器在96.4MHZ 下测量。

您能否提出导致此行为的原因或提供其他故障排除建议?