请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDCLVP111 您好、团队寻求您对此问题的支持。

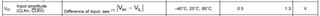

在我们的设计中使用 CDCLVP111、我们将在 Hyperlynx 中运行一些仿真。 我们将遵循图8中的设置。 当我们对其进行仿真时、接收器的摆幅仅为1Vpp、仅足以满足所需的+/-500mV 输入(第6.6节参数 V_ID)、这是否意味着该芯片不能用于驱动另一个 CDCLVP111?

https://www.ti.com/lit/ds/scas859f/scas859f.pdf

谢谢你。

-Mark