请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04832EVM 大家好、

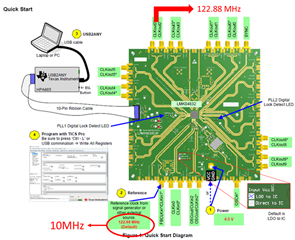

关于默认设置中的步骤2:从信号发生器或其他源将参考时钟连接到 CLKin1*端口。 默认配置使用122.88MHz。

确切的频率和输入端口(CLKin0/CLKin1)取决于编程。

如果我们希望在 CLKIN 端口上使用10MHz 外部源、并且希望得到 CLKOut = 122.8MHz、还 应确保锁定这两个频率。

TICS PRO 上的设置是什么?

谢谢。