请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

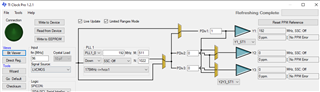

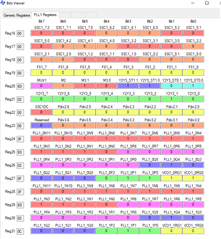

器件型号:CDCE925 我目前正在使用 CDCE (L) 925来生成系统时钟。 输入为96MHz、Y1上的目标输出为192MHz。 到目前为止、我可以获得与输入时钟匹配的输出、或让 Pdiv1对其进行分频。 但是、我无法使乘法器在 PLL1配置寄存器中工作。 我已完成代码设置、其中偏移量在每个配置中表示为数字。 我认为我已经写入的寄存器应该增加频率、但是无论我如何配置 PLL1寄存器、我都不会观察到任何变化。

谢谢、

Kyle

# input clock selection & set slave address to 0 self.pll.NO_BLOCK.GENERIC_CONFIG1.CONFIG1.value = 0b00001000 self.pll.NO_BLOCK.GENERIC_CONFIG2.CONFIG2.value = 0b00111100 self.pll.NO_BLOCK.GENERIC_CONFIG3.CONFIG3.value = 0b00000010 # Y1 output state selection self.pll.NO_BLOCK.GENERIC_CONFIG4.CONFIG4.value = 0b01000010 # FS1_x frequency selection self.pll.NO_BLOCK.PLL1_CONFIG3.CONFIG3.value = 0b00000000 # PLL Mux settings self.pll.NO_BLOCK.PLL1_CONFIG4.CONFIG4.value = 0b11101101 # Y2Y3_x output state selection self.pll.NO_BLOCK.PLL1_CONFIG5.CONFIG5.value = 0b00000010 # # PLL1_0 multiplier/divider for frequency self.pll.NO_BLOCK.PLL1_CONFIG8.CONFIG8.value = 0b00000000 self.pll.NO_BLOCK.PLL1_CONFIG9.CONFIG9.value = 0b01000000 self.pll.NO_BLOCK.PLL1_CONFIG10.CONFIG10.value = 0b00000100 self.pll.NO_BLOCK.PLL1_CONFIG11.CONFIG11.value = 0b00001011 # PLL1_1 multiplier/divider for frequency self.pll.NO_BLOCK.PLL1_CONFIG12.CONFIG12.value = 0b00000000 self.pll.NO_BLOCK.PLL1_CONFIG13.CONFIG13.value = 0b01000000 self.pll.NO_BLOCK.PLL1_CONFIG14.CONFIG14.value = 0b00000100 self.pll.NO_BLOCK.PLL1_CONFIG15.CONFIG15.value = 0b00001011