https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1137928/lmk00338

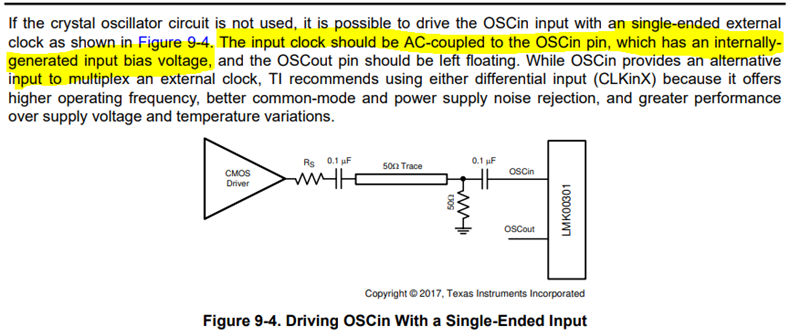

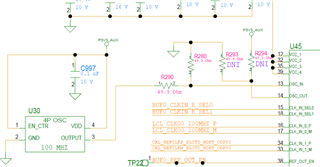

器件型号:LMK003381-我是否会通过直接将 CMOS 振荡器输出应用到 OSCin 引脚来损坏缓冲器内的 OSCin? OSC 的3.3V CMOS 输出通过2 x 49.9欧姆进行2分频并馈送到引脚13 (OSCin)。 未实现交流耦合电容器。

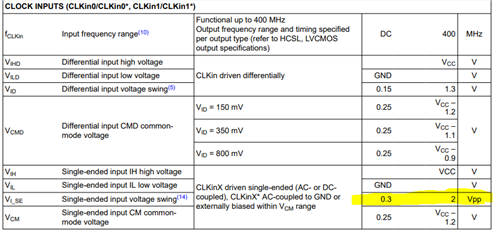

2 -我是否通过以大于1.3V 的摆幅时钟信号馈送这些输入来驱动 CLK_IN_X_P/N? 我在输出端没有得到任何东西、因此我认为可能应该降低输入振幅。

谢谢、

Bahram