大家好、

我对 LMK04828的 PLL1和 PLL2输入时钟之间的关系有疑问 。

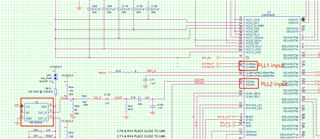

为什么 PLL1输入时钟为 10MHz、而 PLL2输入为100MHz? 如果更改、将会出错?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Nan、您好!

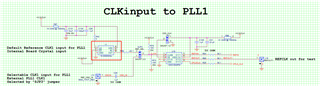

10MHz 是许多测试和测量设备中的通用标准参考信号、因此、能够将板上的 LMK04828的频率锁定在信号发生器、频率计数器、频谱分析仪等其他设备上非常有用

我认为上述答案并不能很好地解释为什么这一系统级设计决策通常发生在许多测试和测量设备中、因此我也会尝试解释这一设计决策。 通常有两种原因可以让人选择使用双环路抖动清除器:

更改 PLL 的输入频率可能会也可能不会产生影响。 如果您将基准输入从10MHz 更改为100MHz、但相位检测器保持相同的频率、则不会发生任何变化。 另一方面、如果您更改相位检测器频率以适应100MHz 基准的更高可能范围、则会改变环路增益和稳定性。 我们有一个计算工具 PLLatinum Sim、可让您自行检查这些更改的影响。

我还将详细介绍我们 的 TI 高精度实验室培训系列 、该培训系列详细介绍了 PLL 设计的基本方面和系统影响。

此致、

Derek Payne

NaN、

您可以仅使用100MHz VCXO、但 VCXO 的频率将为100MHz +ε μ s、其中 ε μ s 是由于温度漂移或控制电压调谐范围而导致的相对于绝对100MHz 的一些小误差。 如果您尝试使用频率计数 器或其他指定为"完美"100MHz (至少用于比较)的仪器测量 PLL 输出频率、 则由于 VCXO 的误差、测量的输出频率将存在 ε* Fout/100MHz 的差异。

请回想一下、大多数仪器都包含一个10MHz 板载基准、此基准可从仪器中输出、也可以连接另一仪器的10MHz 来覆盖板载10MHz。 这是不同仪器之间的行业标准同步机制、这些仪器必须与频率一起工作、例如频率计数器、频谱分析仪、示波器等

通过加入 PLL1、我们可以在频率计数器或其他仪器上获取内置的10MHz 基准振荡器输出、并将其作为 LMK04828 PLL1的基准、从而消除测量误差。 或者、我们可以缓冲一个板载10MHz 基准的副本、并将缓冲后的副本连接到频率计数器上的10MHz 基准振荡器输入。 然后、通过将 VCXO 锁定到 PCB 上的10MHz 基准、10MHz 基准的误差对于 PLL 和频率计数器都是常见的。 我们可以将10MHz 直接连接到 PLL2、而忽略 VCXO 和 PLL1、但相位检测器频率将降低一个数量级、而带内 PLL 性能将降低10dB。 如果没有 PLL1、我们无法将 VCXO 锁定到外部基准。 我们可以添加一个缓冲器/分频器来进行10分频、并将 VCXO 参考非板载传输到我们的仪器、同时为 PLL2... 但这需要大量额外的器件、但仍然无法将 VCXO 锁定到外部仪器的10MHz 基准。

值得注意的是、通常10MHz 基准具有非常好的近端噪声(可能高达1kHz)、但有时与 VCXO 相比、该仪器的10MHz 基准具有非常高的本底噪声。 因此、在这种情况下、PLL1仍然经常用作抖动清除器、即使在将 VCXO 锁定到外部基准并提高 PLL2处的相位检测器频率的同时也是如此。

此致、

Derek Payne

NaN、

输出(推挽)类似于标准 CMOS 输出驱动器、逻辑高电平= 3.3V、逻辑低电平= 0V。 输出反相(推挽)是一样的、但反相:逻辑高电平= 0V、逻辑低电平= 3.3V。

输出(开漏)假定使用了一个外部上拉电阻器。 当 I/O 返回到微控制器/FPGA/等时、漏极开路最有意义 利用2.5V 或1.8V I/O、因为针对逻辑高电平信号、上拉电阻器可连接到编程器 I/O 电源、而不是器件内部3.3V 电源轨。 如果回读总线必须与其他器件共享、开漏也很有用。

此致、

Derek Payne

是的、这是数据表中的错误。 有三个对应于 SPI_LOCK 域的寄存器、用于设置要访问的第13位。 我将把它放在下一个修订版本中需要修复的项目列表中。

[引用 userid="484221" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1027352/lmk04828-the-relationship-between-the-input-clocks-of-pll1-and-pll2/3847151 #3847151]1)如果使用推挽式、是否可以通过 FPGA 中的 ILA 内核调试该信号?是的、这应该是可能的。 我不是完全确定 ILA 内核是如何实现的、但是一旦 I/O 上的任何信号被锁存到 FPGA 寄存器中、它应该能够监控这些信号。

[引用 userid="484221" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1027352/lmk04828-the-relationship-between-the-input-clocks-of-pll1-and-pll2/3847151 #3847151"] 2)和"SPI readback ",这意味着 LMK04828的 SDO (读取数据)? [/报价]是的、SPI 回读输出类型对应于 SDO 回读数据。

[引用 userid="484221" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1027352/lmk04828-the-relationship-between-the-input-clocks-of-pll1-and-pll2/3847151 #3847151"]顺便说一下,我想使用 SPI 4线模式。[/quot]只要 GPIO 中的一个配置为 SPI 回读、SPI 4线模式就会激活。 请注意、从技术上讲、可以同时使用3线和4线模式;如果要使用4线模式并禁用3线模式、请确保 SPI_3Wire_DIS=1 (这应该是默认值)。

此致、

Derek Payne