Other Parts Discussed in Thread: CDCLVD1208

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDCLVD1208 您好!

我需要帮助我检查 CDCLVD1208时钟缓冲器的设计。

1) 1)输入时钟为100MHz LVDS 差分时钟类型、

2) 2)扇出 8通道 LVDS 输出时钟、我使用7通道 LVDS 输出时钟、 (5通道 LVDS 时钟类型、2通道 LVPECL 时钟类型)

3) 3)我的问题:

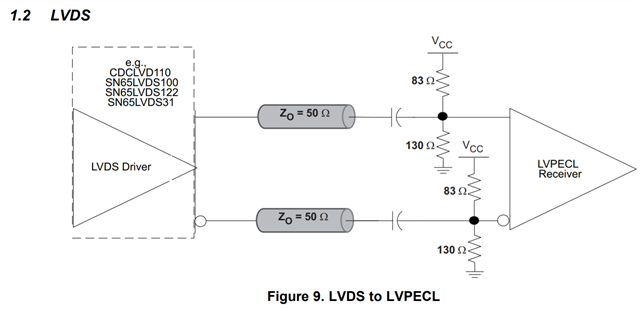

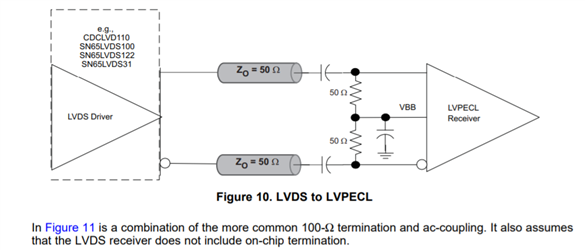

我们参考 TI 的一些文档、将上拉电阻器添加到 VCC、并将下拉电阻器添加到 GND、将 LVDS 时钟类型转换为 LVPECL 类型;

如何选择下拉和上拉电阻器以及 VCC 的值?