尊敬的:

对于正在开发的项目、我们使用 ZCU102评估套件(包括 Zynq Ultrascale+ ZU9EG)为演示器进行开发。

为了将射频开关 从 50MHz (最大占空比为50%)驱动到~ 3.3MHz (占空比为3%)、我们使用 FPGA 的 LVDS 接口。

我一直在寻找具有一个输入和多个输出的缓冲 LVDS、 我找到了 TI 的 LMK00306。

使用多个 LMK00306 (数量= 5) 同时驱动15个射频开关(有裕量)。

每个 LMK 00306都有一个由 FPGA 生成的同步 LVDS 信号。

对我们来说、时序 Trise 和 Tfall 非常重要。 对于 TRR 和 TF 为300PS 的 LMK00306 、这是可以接受的。

我希望评估最慢和最快控制信号之间的最小/最大延迟、以了解裕度。

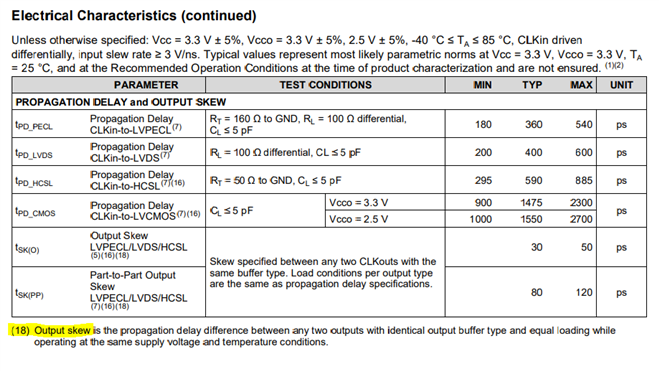

它具有占空比规格(数据表第9页)、对于50%输入时钟占空比、该规格在45%至55%之间。 和输出偏斜时序。

如何理解 LMK00306数据表第9和13页中有关"输出时钟占空比"和"占空比偏斜"的这些信息?

对于 LMK00306输入端的信号,我在输出端可以找到什么信号?

有什么延迟? 谢谢。

此致。

Arnaud Chopin

e2e.ti.com/.../Uses_5F00_Case.pdfe2e.ti.com/.../LMK00306_5F00_Pages9and13.pdf