设计中的系统要求相对较快地更改频率。 我正在尝试确认该组件将符合我在该组件上的规格、即将命令频率达到100Hz。 在数据表上列出的时间内、尤其是在使用完全辅助模式时、该部件是否达到此精度。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

设计中的系统要求相对较快地更改频率。 我正在尝试确认该组件将符合我在该组件上的规格、即将命令频率达到100Hz。 在数据表上列出的时间内、尤其是在使用完全辅助模式时、该部件是否达到此精度。

尊敬的 Kevin:

在全辅助模式下、VCO 校准被绕过、需要写入 VCO 内核、VCO_DACISET 和 Capcode、以便在读取寄存器后更改频率。 因此、如果我们写入正确的值、它将锁定到所需的频率、而不会出现任何精度问题。

请检查以下校准应用手册是否对您有所帮助。

简化射频合成器 VCO 校准并优化 PLL 锁定时间(修订版 A)

此致、

Ajeet Pal

尊敬的 Kevin:

在全辅助模式下、VCO 校准(数字校准)时间为 5微秒、这将使频率保持在+/-10MHz 范围内。 稍后的模拟环路带宽将使频率稳定在 Hz 范围内、其稳定时间取决于模拟锁定时间。 因此、要回答您的问题、 所需的频率将在100Hz 内趋稳、但该时间将取决于模拟锁定时间。

通常在数据表中以及在+/-10kHz 范围内的频率稳定所述的测量锁定时间。

谢谢!

此致、

Ajeet Pal

尊敬的 Kevin:

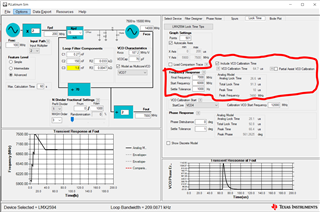

为了根据环路滤波器带宽、工作频率、容差和其他受控参数估算锁定时间、您可以使用 PLLatinum Sim 工具。 这将有助于提供在所有锁定时间和模拟锁定时间内计算得出的值。

示例 如下所示:

此致、

Ajeet Pal

仍然尝试决定答案是什么。

答案:

在全辅助模式下、VCO 校准被绕过、需要写入 VCO 内核、VCO_DACISET 和 Capcode、以便在读取寄存器后更改频率。 因此、如果我们写入正确的值、它将锁定到所需的频率、而不会出现任何精度问题。

似乎它回答了这个问题,但后来的线程显示,在5微秒内,完全辅助模式下无法达到所要求的频率设置,而是达到了一定的时间长度。 如果该器件无法在发出命令后达到5 μ s 内的精确频率、是否有替代器件可以实现?

尊敬的 Kevin:

这是一个模拟 PLL/VCO、VCO 将只能以闭环方式锁定到基准时钟。

该器件的芯片内有7个 VCO。 VCO 校准用于确定哪个 VCO 的 Capcode 和 DACISET 最适合目标频率。 这是粗调。 它依靠 PLL (闭环)将 VCO 微调到精确的频率。 因此、VTune 电压可能会变化。 例如、VCO 校准在25°C 时完成。 现在温度已升至60C。 您无需重新校准器件、VTune 将进行更改以适应温度影响。

我不知道5µs 中的任何宽带合成器都无法支持 Δ Σ 锁定时间。 直接数字合成(DDS)器件可能能够实现此响应时间、但我认为在该频率下不可用。

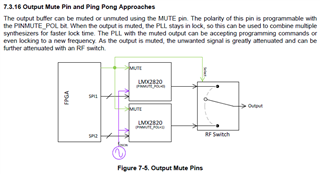

一种可能的方法是交替两个合成器、开关时间将在纳秒范围内。