请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

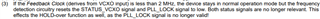

器件型号:CDCM7005-SP 大家好、

VCO 指示器:

输出频率:384MHZ

输出功率:1.5 ~ 4.5dBm

调谐电压0.5 ~ 2.5V

电压控制灵敏度:3-6MHZ / V

PLL 设置:

输出时钟:384MHZ、96MHZ、24MHZ

参考时钟:100MHz

℃:六个电路板中两个电路板的 CDCM7005-SP 的 STATUS_VCXO 引脚指示低至-10 μ V 的异常、锁定指示也异常。 然而、测试芯片的384MHZ、96MHZ 和24MHz 输出时钟没有问题、这证明 PLL 锁定正常、只有状态指示异常。 室温下没有问题。

环路带宽更改为100k、问题仍然存在。

问题可能出在哪?

此致、

罗美