主题中讨论的其他器件: LMX2594

我们一直遇到高于仿真输出的相位噪声问题、我们已将源范围缩小到 LMX2820。 作为测试、我们采用了10MHz CMOS 输出晶体、并将器件配置为输出6GHz。 10MHz 基准具有以下相位噪声规格:

100 Hz -123dBc/Hz

1000 Hz -142dBc/Hz

10000 Hz -149dBc/Hz

100000 Hz -150dBc/Hz

1000000 Hz -150dBc/Hz

10000000 Hz -150dBc/Hz

在输出频率为6GHz 的 PLLatinum 仿真(使用二阶环路滤波器:C1 3.3nF、C2 47nF、R2 100 Ω)中、我们得到的仿真噪声输出为:

100 Hz -67dBc/Hz

1000 Hz -86dBc/Hz

10000 Hz -93dBc/Hz

100000 Hz -93dBc/Hz

1000000 Hz -119dBc/Hz

10000000 Hz -151dBc/Hz

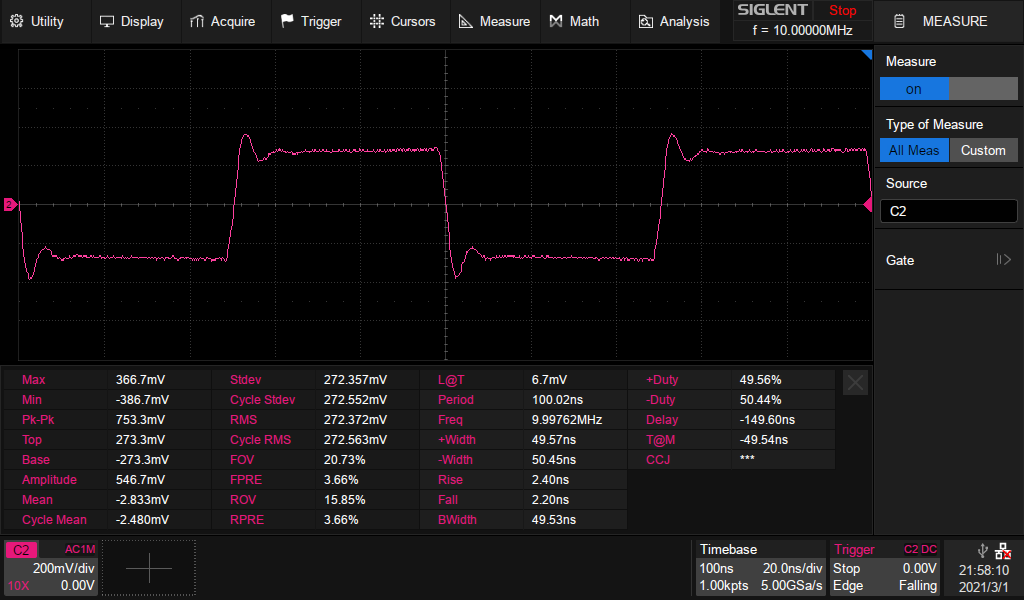

但是、当我们测量输出时、我们在1kHz 至100kHz 范围内得到~20dB 的更高数字:

100 Hz -60dBc/Hz

1000 Hz -66dBc/Hz

10000 Hz -74dBc/Hz

100000 Hz -102dBc/Hz

1000000 Hz -120dBc/Hz

我知道这不是一个理想的设置、但这是一个用于识别高相位噪声源的测试。 在实际设置中、我们有一个高端100MHz 参考源馈送到 LMX2594、后者馈送到 LMX2820。

仿真文件项目(PLLatinum 和 TICS Pro 文件)、参考噪声、原理图和测量数据随附以供参考。