您好!

我们观察到、通过寄存器写入来重置 LMX2492 PLL 失败、故障率大约为1%。

我们通过对寄存器2执行以下写入操作来重置器件:

PLL_WRITE (0x02、0x04);//寄存器复位(值5存在相同的问题、即不断电)

DELAY_ms (1); //延迟

PLL_WRITE (0x02、0x01);//将 PowerDown 设置为'01'(稳定亮起)

_DELAY_ms (1); //延迟

{...} //加载 MUC、FRAC、CPM、计数寄存器等...

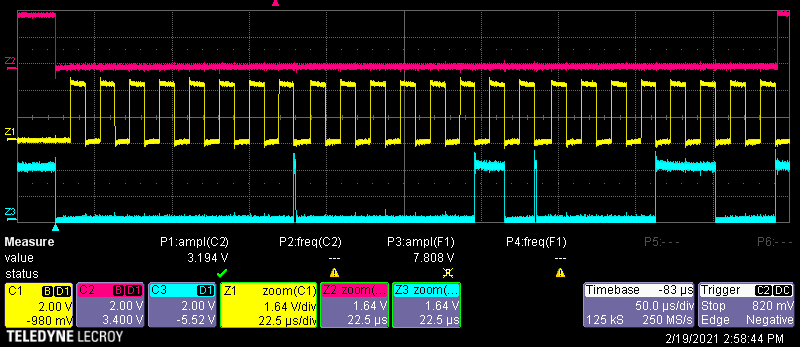

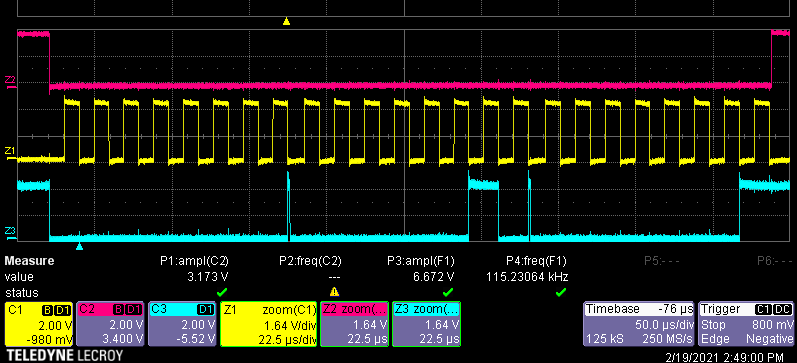

我们将无法通过从 MUXout 接收频率信号来进行复位定义、MUXout 设置为"输出 N 分频/4"(MUXout_MUX=19、MUXout_PIN=2、由 PLL_WRITE (0x27、0x9A)设置)。 相反、MUXout 为恒定高电平。

我们还观察到、在失败状态下、保留寄存器46..55 (0x2e.0x37)读取0x00、而这些寄存器在成功复位和初始化后读取非零值。 记录寄存器在任何状态下读取合理值。

我们在不减少故障的情况下增加了上述代码中的延迟。

我们已将 Vcc 增加至数据表最大值3.45V、而不会减少故障。 四个3.3V 电源引脚中的每一个都通过 LC 网络供电,该网络具有一个330欧姆(100MHz 时)的铁氧体磁珠与靠近器件的一个1nF 和一个100nF 电容器串联,所有四个残桩均由具有附加电容器的单个3.3V LDO 供电。

复位失败通常可以通过重复上述复位过程来解决。

导致此行为的原因是什么?

谢谢!