主题中讨论的其他器件: LMX2492、 LMK04816、 LP5912

您好!

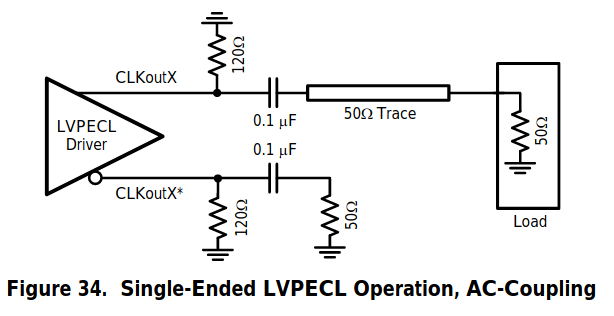

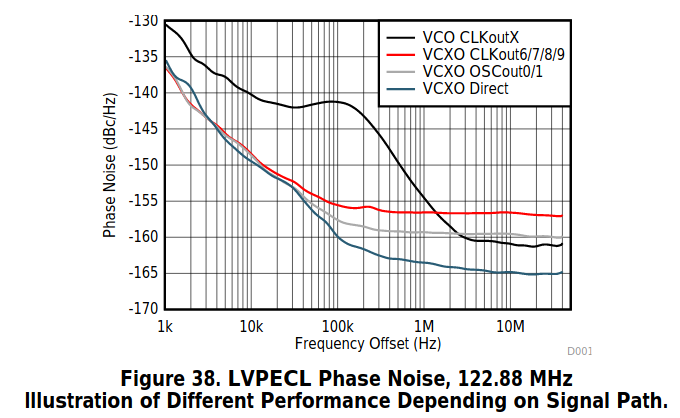

LMK04906数据表在第108页提供了相位噪声图、比较了 OSCout/CLKout VCXO 和 VCO 相位噪声性能。 此测量是否如第91页(图34)所述? 即、该数字是单端还是差分测量(使用外部平衡-非平衡变压器)?

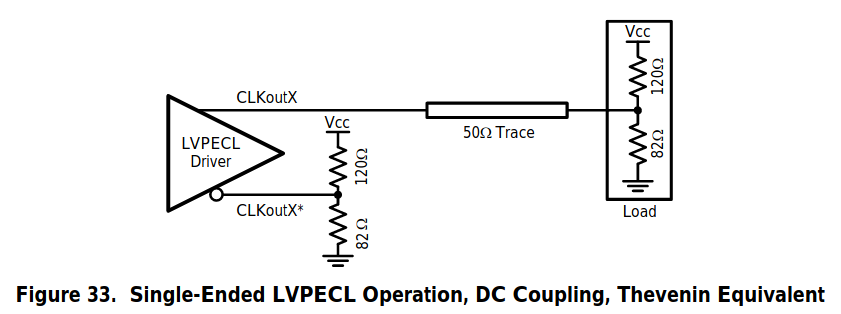

我们将 LMK04906设计成了一款产品、但无法实现与数据表中给出的 OSCout/CLKout 输出相同的本底噪声性能。 但是、我们将 LVPECL OSCout0输出用作两个单端输出、如图33 (第91页)所示。 我们现在要问我们是否可以对它做些什么。

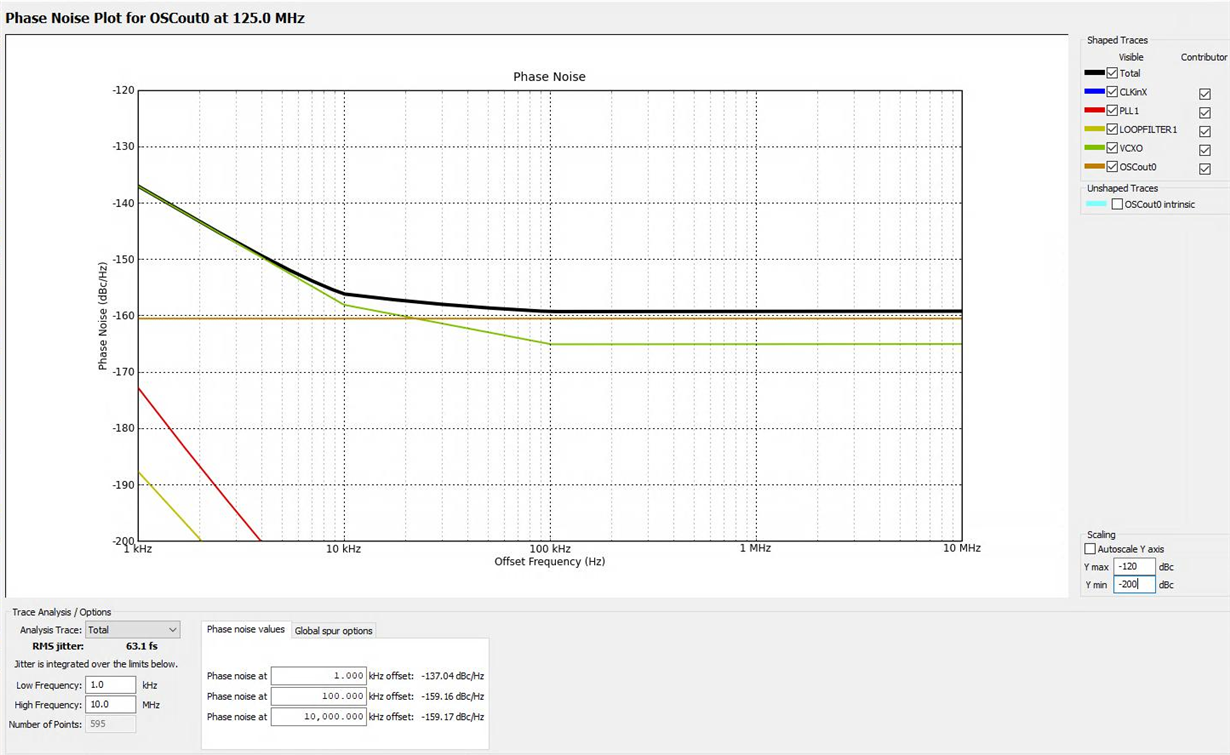

作为本底噪声、我们能够达到大约-150dBc/Hz。 参考时钟是具有 LVCMOS 输出的125MHz 超低噪声晶体振荡器(1kHz:-137dBc/Hz、10kHz:-158dBc/Hz、100kHz:-167dBc/Hz、floor:-169dBc/Hz)。 根据仿真、我们应该在旁路了 LVPECL 标准和分频器的 OSCout0输出上达到接近-159dBc/Hz。

如果仿真数字在我们的单端场景中是真实的、那么有什么提示可以尝试降低本底噪声? 哪些电压引脚可以提高芯片的本底噪声?

此致、并提前感谢您