尊敬的团队

我们计划在仅 PLL2模式下使用 LMK04616、同时在 ZDM 和纯缓冲模式下使用 OSCin。 我们有一些困惑、如下所示:

在 ZDM 模式下、反馈通道是 CH7/8还是 CH 6/9?

2.在 ZDM 模式下、也需要同步所有输出分频器、我们的器件是否支持?

3.在 ZDM 模式下、输入和反馈通道之间的相位误差是多少?

4.在任何情况下 OSCout 将始终与 OSCin 具有相同的频率?

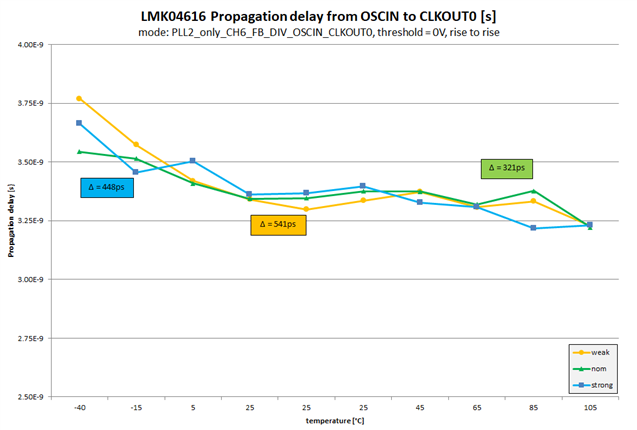

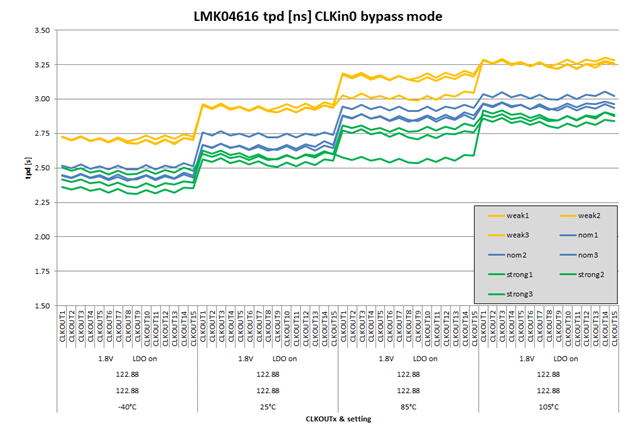

5.在缓冲模式下,OSC IN 至 Clkout 传播延迟,最小值和最大值?

6.在缓冲模式下、部件间偏移、最小值和最大值?

谢谢

沈俊