主题中讨论的其他器件:LMK04828、、

需求:

调制和解调板主要使用 BPSK 信号来实现高精度测距。 信号的芯片速率为100MHz、占用带宽为200MHz、载波频率为1.2GHz。 要求每个上电参考时钟与系统每个部分的相位一致、并且具有可重复性、也就是说、有一个确定性相位关系。 外部基准信号的频率为100MHz、这是氢原子时钟频率加倍后的信号。 稳定性和相位噪声非常好。 因此、在选择时钟芯片时、不要选择具有外部晶体振荡器的双环路 PLL。 时钟芯片会使输入基准信号索引(如7044)恶化。

dac9172的采样率为9.6GHz、BPSK 载波为1.2GHz。 FPGA 提供给 DAC 的两个基带数据速率(I 通道数据和 Q 通道数据)分别大于300MHz 和100MHz 的整数倍。

接收板的 ADC 采样率约为3GHz (待定)。 目前、AD9208暂时确定、BPSK 载波为1.2GHz。 抽取后、FPGA 的采样率输出约为300MHz ~ 500MHz 范围内的主频率(例如499.99mhz、333.49mhz)。

计划:

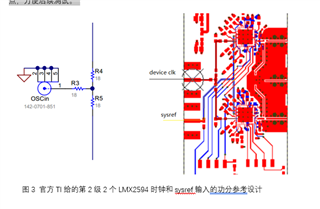

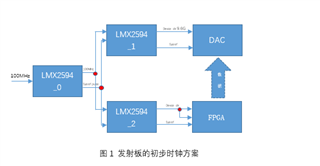

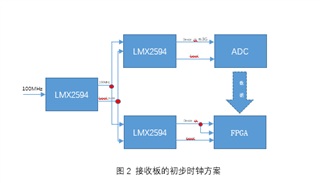

目前可能的时钟方案是使用三个 lmx2594芯片来实现系统。 此方案由 TI 官方提供(信息名称为"多个 PLL 合成器的相位同步参考设计"、我已在该组中发布)。 在该参考设计中、需要为同一时钟芯片提供第二级中两个 lmx2594芯片的时钟输入和 sysref 同步脉冲、以便实现系统、两个 lmx2594芯片的输入和输出时钟具有确定性相位。 对于此类应用、官方建议使用 lmx2594evm 或 lmk04828evm 来提供此时钟和 sysref、但当 lmk04828生成主频时、相位噪声会严重恶化、因此可以选择 lmx2594evm 作为第一级时钟芯片、如图1和图2所示。

对于我们的应用、如果 lmx2594在类别3模式下工作、即在 lmx2594输入100MHz 和输出之间没有整数倍关系、那么 lmx2594_ 1/ LMX2594_ 2需要使用 lmx2594_ 0提供严格的时钟和同步信号、 用于确定第二级输入和输出之间的相位关系 lmx2594、lmx2594_ 0提供时钟和同步信号并需要相位对齐。

注意:当 lmx2594在 category1和 category2模式下工作时、如果第二级的两个 lmx2594同步、则输入参考频率范围为0 ~ 1400mhz; 当 lmx2594在类别3模式下工作时、如果第二级的两个 lmx2594同步、则输入基准频率范围为0 ~ 100MHz;(可找到 lmx2594芯片手册的 P11表和图27。)

现有问题

目前,问题的关键在于图1和图2中红点的位置是通过直接工作共享还是通过使用固定延迟的时钟缓冲器来分配的。 官方评估板使用直接功率共享方法在左侧的两个红点评估 lmx2594、分配0的输出时钟和 sysref、并通过控制线长来实现同步、如图3所示。 如果使用缓冲器、缓冲器引入的抖动应小于1ps (许多大约为100fs)。 目前,我们需要进一步确定使用哪种方法。 最好由 TI 的工程师来确定。 目前、我们是否可以通过缓冲器或功率共享来设计冗余? 最好为时钟链路的每个节点设置测试点、以方便后续测试。