主题中讨论的其他器件: AFE58JD18

通过使用差分探针(10:1)查看 LMK04821 SDCLKout 的输出 、我可以看到以下情况。

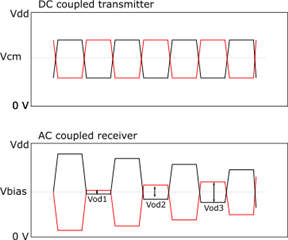

DCLKout 输出看起来不错、波形也不错。 SDCLKout 输出、提供16.6MHz sysref

看起来"糟糕"。 是否有我应该以不同的方式设置的内容?

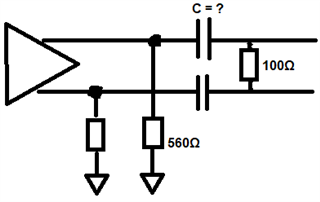

在 LMK04821的输出端、我们放置了560R 分流器、然后将交流耦合到目标端、并在那里放置了100R 端接(实际上是 AFE58JD18的 sysref 输入)。

有什么想法吗?

此致、

ED