您好!

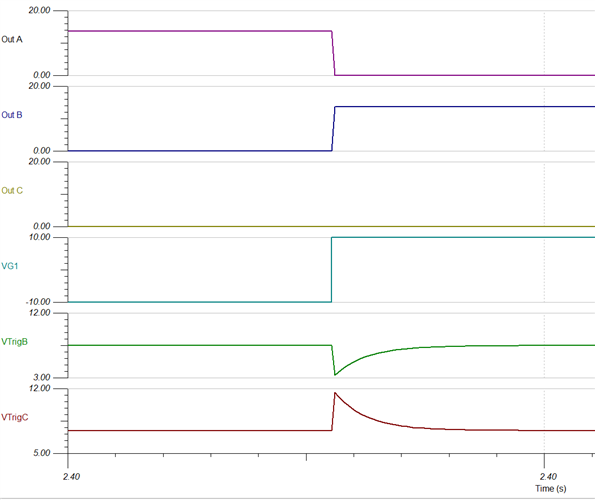

我注意到、SE555的数据表图22中的顺序计时器电路违反了其 TRIG 引脚的绝对最大额定值。 你同意我的说法吗? TRIG 引脚的绝对最大额定值被定义为 VCC (Max)、但是当前一级的 OUT 引脚电压上升时、一个 RC 电路后的引脚波形超过 VCC。

您对此有什么权变措施吗?

此致、

横田新一

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

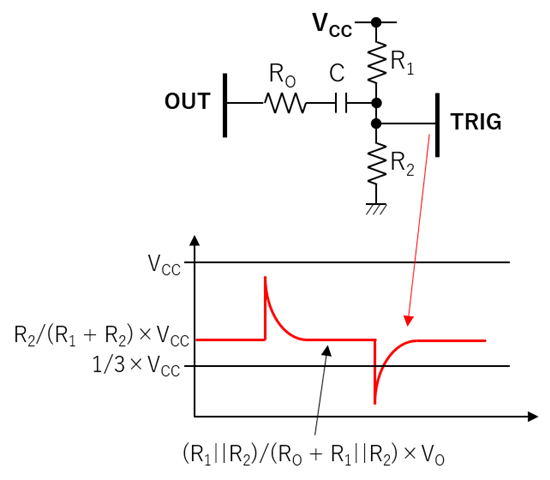

很棒的收获! 我也在仿真中看到了这一点。 我已在仿真中将0.001uF (1nF)降低至1pF、此外还形成了分压器以降低 dv/dt。 我也在帖子的底部为您附加了仿真。

对于1nF 的情况、我看到仿真中的电压尖峰高达26.31V (数据表电路)。 这似乎是由 C*dv/dt 引起的。 通过降低这两个因素、我能够平滑触发线、如下面第二个仿真中所示。

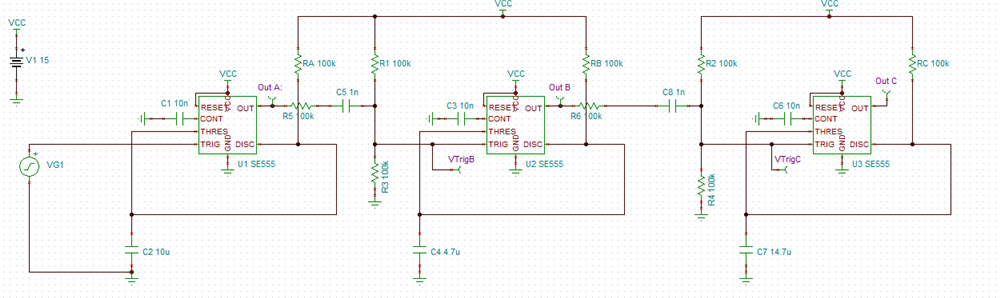

数据表电路

我的修订版电路及以下仿真:

Chris San、

感谢您的反馈。 但是、我恐怕会说、我认为 TRIG 引脚上的正尖峰不会消失。 RC 电路的 kΩ kΩ 为50ns (= 1pF×(100 μ s || 100 μ s))、非常小、我想由于时间刻度较大(在一秒范围内)、它不会显示在仿真图中。 此外、我认为1pF 电容器对于实际的 PCB 来说是不现实的、因为它与 PCB 上的寄生电容一样小。

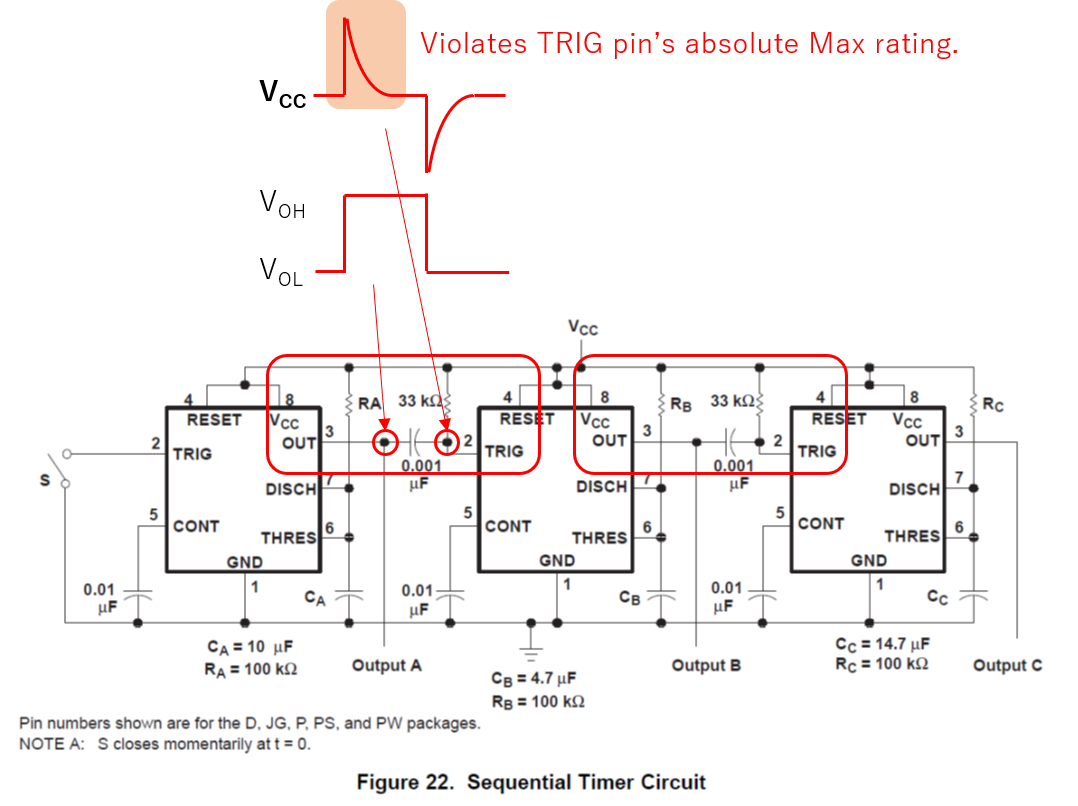

我提出了以下电路。 我在前一个 SE555级的 OUT 引脚上添加了一个 RO、以衰减 VO 振幅、使其正尖峰不会超过 VCC。 你怎么看? 但是、如果电路投入生产、我需要考虑组件值的变化。

此致、

横田新一

Shinichi-San、

是的、这看起来非常合理。 我也这样做了、看起来不错。 您可以正确地看到、PCB 寄生效应在使用较小电容器时发挥更大的作用。 我用它来演示目的是为了看到 C*dv/dt 的降低。

您的解决方案看起来很棒! 我对组件进行了切换、使电容器为1nF、并选择了100k 进行测试。 当然、这些会随电路中的尖峰而变化。 电容越大,但对寄生效应的影响就越小,C*dv/dt 越大,尖峰就越大。 在电路板上为 R 和 C 设置这些占位符将使您能够灵活地进行相应调整。