请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2485E 你(们)好。

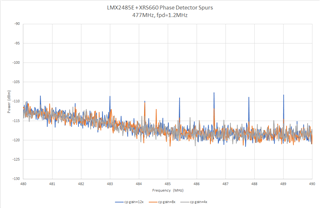

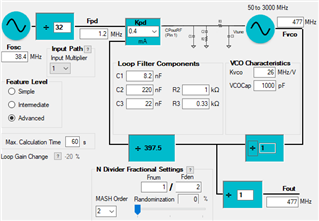

我设计了一个 PLL 来与我的 VCO 配合使用、到目前为止、大多数事情都很好。 我遇到的一个问题是相位检测器杂散、尤其是在使用更高的 CP 电流时。 是否有任何已知技术可供我分享、以尽量减少杂散? 我尝试单独提供两个 VDD_RFAS、但没有注意到任何改进。

我已经使用不同的 CP 增益测试了这些杂散,我知道环路滤波 器带宽会随着较低的 CP 增益下降,这可能会造成。