主题中讨论的其他器件: PLLATINUMSIM-SW、LMK03318

您好!

我在我的设计中使用的是 LMK03806。 设计详细信息如下所示

FOSCin = 10MHz

要生成的输出频率= 204MHz

我计划使用 Fvco = 2448MHz。

请建议 PLL 分频器值以获得最佳性能。

此外、还阐明 了相位检测器频率对总体抖动性能的影响。

提前感谢、

Pratiksha

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我在我的设计中使用的是 LMK03806。 设计详细信息如下所示

FOSCin = 10MHz

要生成的输出频率= 204MHz

我计划使用 Fvco = 2448MHz。

请建议 PLL 分频器值以获得最佳性能。

此外、还阐明 了相位检测器频率对总体抖动性能的影响。

提前感谢、

Pratiksha

Pratiksha 您好、

LMK03806包含一个倍频器、因此可用的最高参考频率为20MHz。 VCO 频率必须为2448MHz、因为其他有效分频不能产生204MHz。 GCD (2448、20)= 4MHz、因此您将启用基准倍频器、将 R 分频器设置为5、并将总 N 分频器设置为612。 有效的预分频器/N 分频器组合包括:

一个值与另一个值相比没有很大的好处、但通常我们建议使用最高的预分频器值来减少使用的 N 分频器级总数。

通常、相位检测器频率越高、带内噪声越低、PLL 带宽也越高。 请注意、我们在 PLLatinum Sim (PLLATINUMSIM-SW)中提供了 LMK03806模型、可用于对不同相位检测器频率、电荷泵增益、环路滤波器带宽等的影响进行建模

此致、

Derek Payne

Pratiksha、

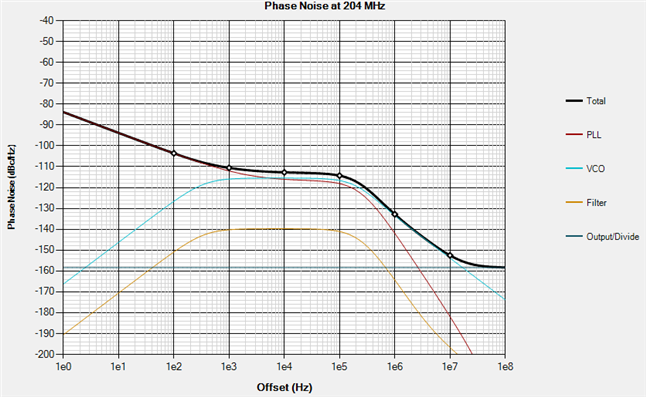

我同意、4MHz 环路滤波器肯定会阻止您实现比我预期的更好的 RMS 抖动数。 我得到大约1200fs RMS 12k-20M @ 204MHz 载波、其中 C1=10pF、C2=56nF、R2= 8.2kΩ 680Ω 200Ω Ω、并且集成组件设置为 C3=18pF、C4=10pF、R3=8 Ω、R4=8 Ω。 由于相位检测器频率较低、PLL 噪声是主要影响因素。 我认为您无法在这一范围之外进行优化、因为由于您的器件选择和基准/输出频率要求、您会遇到一个基本限制。

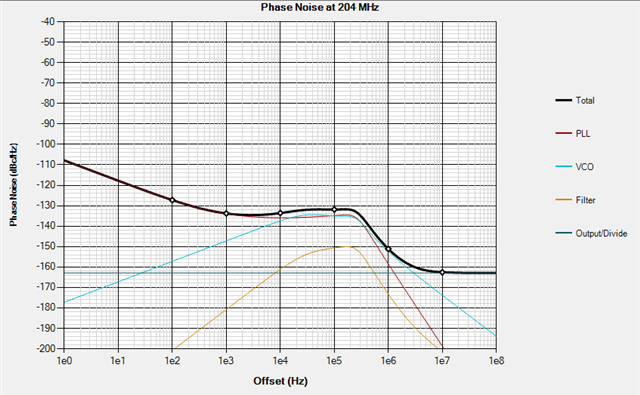

我想您最好使用 LMK03318等具有成本优势的器件、它具有支持20MHz 相位检测器的更高 VCO 频率和有助于降低 PLL 噪声影响的更高电流电荷泵。 如果没有太多的优化、5100MHz VCO、N 分频器=255、20MHz 相位检测器、6.4mA 电荷泵增益、25的输出分频器、我将得到大约175fs RMS 12K-20M @ 204MHz 载波。 C1 = 450pF、C2 = 4.7nF、R2 =~1.2kΩ Ω、C3 = 10pF、R3 = 18Ω Ω。

此致、

Derek Payne