大家好、

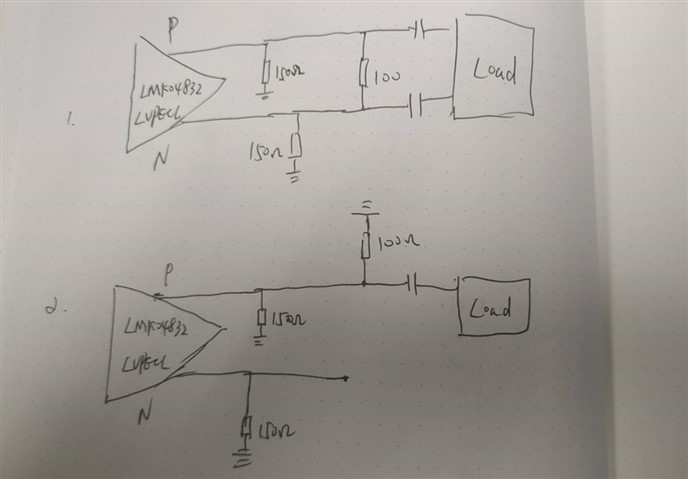

我有一个问题、我们是否只能使用 LVPECL 一个输出端口? 如下所示的匹配电路。 由于电路板布局是固定的、因此输出只能设置为差分输出格式无法设置为 LVCMOS。 那么、我想确认下面显示的电路2是否可以正常工作? 谢谢!

B.R.

Zhizhao

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Zhizhao 您好、

[报价 userid="423121" URL"~/support/clock-and-timing/f/clock-timing-forum/994065/lmk04832-lvpecl-output-format-only-use-one-port ]输出只能设置为差动输出格式无法设置为 LVCMOS[/QUERP]意味着支持 LVCMOS 的输出连接到您的负载? 因为否则该电路将支持 LVCMOS。

--

实际上、顶部的电路也不是交流耦合 LVPECL 的正常拓扑。 发射器电阻器(150欧姆)和负载上的100欧姆端接之间应该有电容器。 不过、您只需考虑一个桥臂的发射极电阻器与另一桥臂的负载+发射极电阻器并联的影响即可。 因此、如果您将150欧姆发射极电阻器增加到240欧姆、那么它的行为实际上就像您使用120欧姆发射极电阻器一样。 因此、如果您的目标是150欧姆、您可以使用高于240欧姆的发射极电阻器。

如果您想运行单端、可以只使用顶部原理图(使用240欧姆或更高的发射极电阻器)并移除负载一侧的电容器。 例如 N 侧。 这是我的建议。

底部的原理图不好。 基本上、您现在在一侧具有发射极电阻器、更低的一侧为150欧姆|| 100欧姆。 100欧姆远低于50欧姆、可实现良好的单端终端。

73、

Timothy

您好、Timothy、

谢谢。 实际上 、这适用于 LMK04832 OUT 12。 之前的 out12是支持 LVPECL 的差分负载。 但现在我需要更改为 LVCMOS 负载。 这就是我需要使用 LVPECL 的一个输出端口并连接到 LVCMOS 负载的原因。

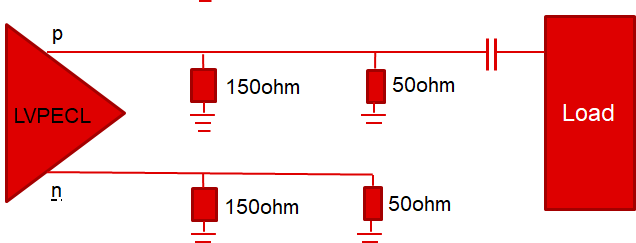

根据我的理解、您意味着、如果只将 LVCMOS 负载连接到 P、我们需要进行如下所示的匹配? 谢谢!

B.R.

Zhizhao

您的 LVCMOS 负载的电压电平是多少? 3.3V LVCMOS? 1.8V LVCMOS?

ODDS 是您将无法通过 LVPECL 满足 VOH 和 VOL。 但是、如果您是这样、则必须(a)移除电容器或(b)将负载侧偏置到适当的电压。

我先前曾建议、如图1所示、实现交流耦合 LVPECL 的正确方法。 发射极电阻器、或通过电容器与100欧姆负载隔离。 您不需要上面所示的电路、因为发射极输出将看到37.5欧姆的直流接地路径。 发射极电阻器应>= 120欧姆。

现在可以像处理与发射极电阻并联的负载一样执行 LVPECL、但在这种情况下、我建议 RE >= 240欧姆。 使用240欧姆时、考虑到实际发射极电阻约为 re ||(RL + re)、有效发射极电阻为120欧姆。 由于它连接到相反的输出、因此比给出的公式更复杂一些。

*我已在我的建议中将此方法用于您的电路。 使用 RE = 240欧姆、差分100欧姆终端、然后交流耦合到 CMOS 负载。 请注意、我认为您不需要这里的 LVCMOS 电容器。 使用0欧姆、然后您将获得来自 LVPECL 的直流时钟-但它可能不符合您所需的 VOH/Vol 规格。 但考虑到您的布局、我认为这是您可以做的最好的事情。

73、

Timothy