Other Parts Discussed in Thread: LMK04832

主题中讨论的其他器件:LMK04832

HII 团队、

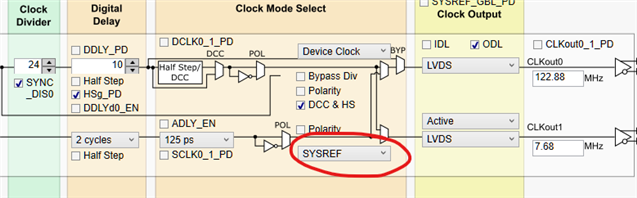

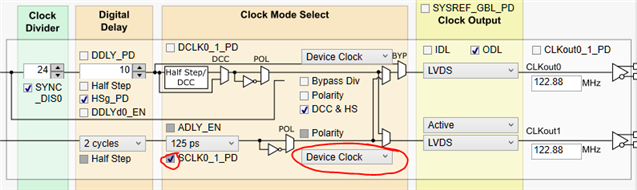

我们使用 LMK04832 EVM 并使用 TICS PRO 工具对其进行编程。 我们 是第一次使用 EVM、为了获得实践经验、我们针对 CLKin1 = 122.88MHz 对其进行了编程并将所有输出配置为122.88MHz、但当我们探测和检查 EVM 输出端口4、5、6、7、12、13时、未提供所需的输出。 我是否可以知道输出不正确的原因? 我已附加编程文件。 我还请你帮助我们纠正这一问题。

--

此致、

基尔萨纳。