大家好。

我已正确配置 LMK04610 IC。 它的两个输入端具有来自 KEYSIGHT 33600A 双通道发生器的40MHz 频率。 我还使用了 VCXO

ABLNO-V-122.880MHz。 nr 5输出上的输出频率约为10MHz (便于测量)、但将来我会将其更改为200MHz。

LMK04610还可以校正缺少的第一个或第二个输入时钟。 它在 PFD 频率的大约1.5周期内(在我的例子中为80kHz -大约15us)切换到保持模式

将 Vcontrol 电压保持在正确的值、然后将信号摆动到另一个源。

选择另一个输入信号后、问题就会开始。 我只想补充一点、当我置位时、在复位 N 和 R 分频器时会发生同样的情况

0x57配置寄存器中的 PLL1_RDIV_SWRST 和 PLL1_NDIV_SWRST 位(3和4)。

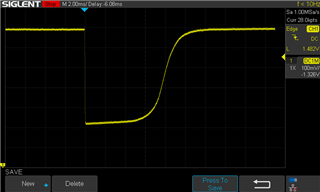

问题是 PLL1缺少一些时钟信号、可以在控制电压示波器上看到这些信号。 我已附上两个示波器屏幕截图。

您可以看到、VCO 调节仅在一个方向上。 因此、VCO 相位仅在一侧发生变化。 集成控制电压对应于100ns 的相位变化(当我设置另一个环路参数时略有变化)。 该值对应于122.88MHz 的约12 clk 或40MHz 的4 clk 输入频率。

我的问题是这是正常情况吗? 是否有任何方法可以初始设置 R 或 N 分频器、而是将其复位? (在保持 R 和 N 分频器也被复位后)我们是否还有其他可能将观察到的行为最小化?

e2e.ti.com/.../LMK04610_5F00_10MHz_5F00_out.tcs

e2e.ti.com/.../LMK04610_5F00_10MHz_5F00_out.tcs