主题中讨论的其他器件:LMK04828、 ADS54J60EVM、 ADS54J60

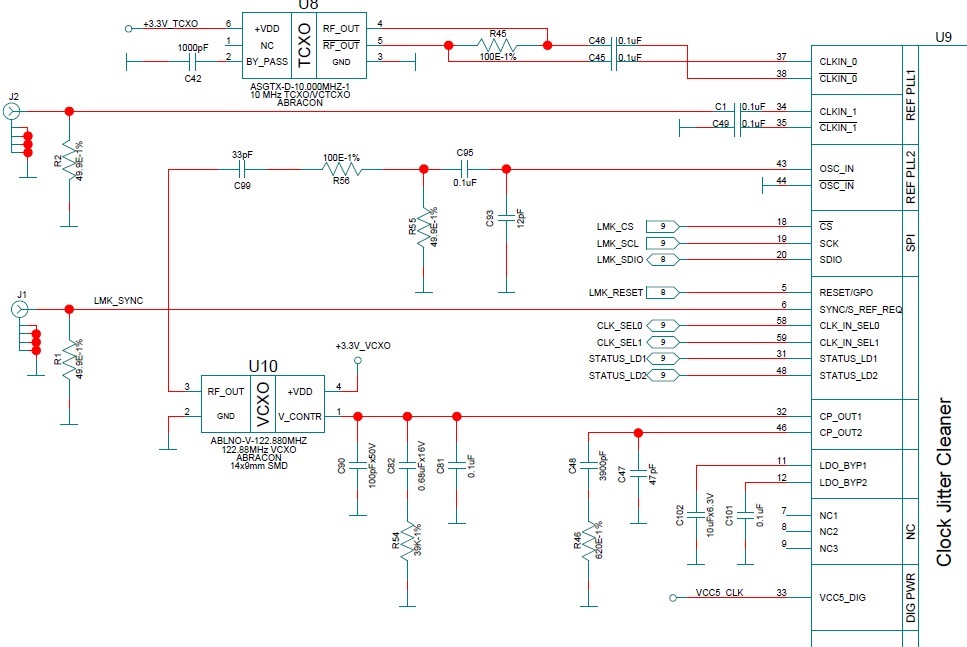

我们在尝试使 PLL1锁定时遇到问题。 随附的是使用的 TCS 文件。 无论使用的是板载10MHz 源还是外部源、PLL1都不会锁定。 此设计基于 LMK04828EVM 板。

一个有趣的注意事项... 当器件被置于时钟分配模式并且一个100MHz 时钟被施加到 CLKIN1时。 没有分频的时钟输出比输入稳定得多。 输入为0.5PPM 稳定、但输出为500ppm。 此外、如果选择了"仅分频器"选项、输出会降至~3.2MHz、并且与时钟并不相似。

请提供任何帮助。