主题中讨论的其他器件: ADS42JB46EVM、 LMK04821、 ADS52J65EVM、 LMK04832EVM、 LMK04832

你(们)好

我们希望在分配模式(两个 PLL 均关闭)下使用 LMK04828、其中源时钟的相位噪声<-154dBc/Hz@1kHz。

在该偏移(至少-148dBc/Hz)下、器件是否能够分配此类时钟而不会显著降低相位噪声?

谢谢、

Daniel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我们希望在分配模式(两个 PLL 均关闭)下使用 LMK04828、其中源时钟的相位噪声<-154dBc/Hz@1kHz。

在该偏移(至少-148dBc/Hz)下、器件是否能够分配此类时钟而不会显著降低相位噪声?

谢谢、

Daniel

Liam、您好!

我已经尝试在 LMK048xx 系列器件处于分配模式的情况下运行多个电路板。 特别是 LMK04832EVM、ADS52J65EVM (LMK04821)和 ADS42JB46EVM (LMK04828)。 与双 PLL 模式相比、性能要差得多、这是一个问题

使用 LMK04832上的相位噪声分析器可以观察到高于-140dBc 的本底噪声增加和更差的近端噪声。 ADC 数据还显示本底噪声增加、SNR 性能差。

时钟源具有上述规格-它基本上是具有正弦输出的超低相位噪声 OCXO。 我尝试将其输出转换为 CMOS (无相位噪声降级)以提高压摆率、但不会影响性能。

PLL 和 SYSREF 电路均断电。 分压器模块被旁路掉。 我在 FIN 输入中试用了双极和 MOS 缓冲器、但不会影响性能。 我真的不知道是什么问题。

可以帮帮我吗?

此致、

Daniel

你(们)好、Liam

基准输入电平应约为10dBm@50ohm。 ADS52J65EVM 在 CLKIN1输入端包含50 Ω 电阻器、因此 Vpp 应为2Vpp (使用示波器进行检查)。

我无法提供.TCS 文件。 基本上、我采用了具有分配模式的 LMK04828的脚本、并使用数据表(PD 两个 PLL、VCO、输入...)进行了检查 并根据我的要求修改了寄存器序列。 我已附加原始脚本。

此致、

Daniel

Daniel、您好!

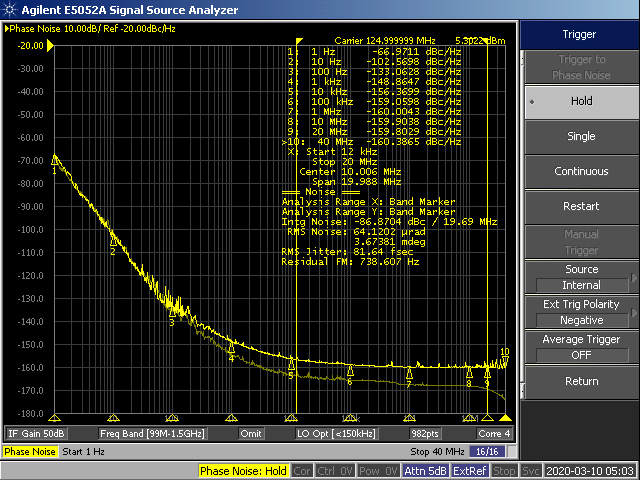

不一定需要对高频输入进行分频以获得良好的性能。 可能会有额外的3dB 总增益、该增益可在较高的偏移下从高质量信号中除以、但需要很大的除数才能意识到、在这种情况下、不相关的噪声改进接近热限值。 请参阅以下内容、了解30fs 基准(存储器跟踪)与 LMK04832 LVPECL 2.0V 分配模式(除以1并启用占空比校正(DCC))的比较、以及显示分布模式下本底噪声约为-160dBc 且1kHz 性能为-148.9dBc/Hz 的跟踪数据:

e2e.ti.com/.../125MHz-Source.txte2e.ti.com/.../125MHz-CLKout0-LVPECL.txt

e2e.ti.com/.../125MHz-Source.txte2e.ti.com/.../125MHz-CLKout0-LVPECL.txt

LMK04828和 LMK04832具有非常相似的输出结构、因此我希望启用 DCC 时1分频的性能结果大致相等。 根据源的质量、可实现优于-148dBc/Hz @ 1kHz 的性能。 仔细检查您的应用中的 LMK04828是否配置为除以1并启用 DCC。

此致、

尊敬的 Derek:

您的测量很有趣。 您能否提供有关使用过的电源(电源、正弦/方形)的更多信息? 使用 LMK048xx 时钟源(SINUS、2Vpp@50欧姆、-156dBc/Hz@1kHz、<-160dBc/Hz 本底)时、我无法实现这种性能。

您能否提供寄存器序列? 我尝试过几种组合、例如旁路分频器、1分频器、DDC、但都没有成功

谢谢你。

此致、

Daniel

Daniel、您好!

根据 LMK04832EVM 原理图、我使用了具有现有单端 CLKin1输入(以及3dB 电阻垫)的 LMK04832EVM。 输入源为 R&S SMA100B、正弦输出为12dBm (因此引脚看到~9dBm)。 我已附上我在下面使用的 TCS 文件。 程序是:

e2e.ti.com/.../LMK04832-125MHz-LVPECL20-CLKout0.tcs

此致、