主题中讨论的其他器件:LMK04208、 CDCLVP1102、

您好!

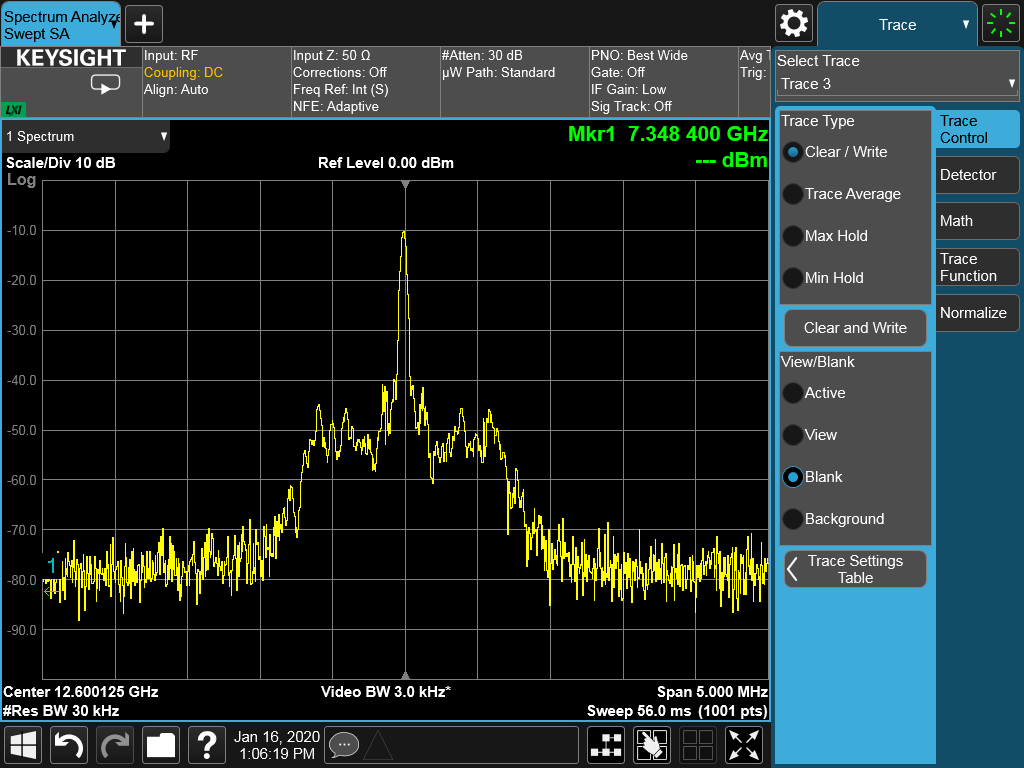

我们看到载波周围调制的高振幅噪声和杂散高达+/-600kHz 左右。 请参阅随附的图片。 并发送 TICsPro 文件以进行我们的配置。

LMK2595由 LMK04208时钟分配芯片生成的122.88MHz 时钟源驱动(LVCMOS 驱动器的单端输出)

然后、该参考信号通过不平衡变压器发送到双路输出时钟缓冲器 CDCLVP1102。 基准信号被发送到2个单独的 LMK2595 PLL 芯片、两个 PLL 都有相似的输出噪声问题。

您是否看到此处使用的参考信号时钟电路有问题或对可能的根本原因有建议?

谢谢、如果您需要其他信息、请告诉我。

最棒的

Cecile

e2e.ti.com/.../LMX2595_5F00_cnfg_5F00_12p6GHz_5F00_122p88M_5F00_Ref.tcs