相关人员

现在、我面临着 LMK03318的一个奇怪问题。

问题在于、系统引导时、LMK03318上的时钟输出不会偶尔发生。

并非每次在所有 LMK03318上都出现此问题。

-。 当系统启动时、输出有时会生成、而不会生成、即使样本相同也是如此。

-一些同时在开发板上制造的板具有并且没有针对每个板的时钟输出

对于不产生输出的电路板、以下修改会产生时钟输出:

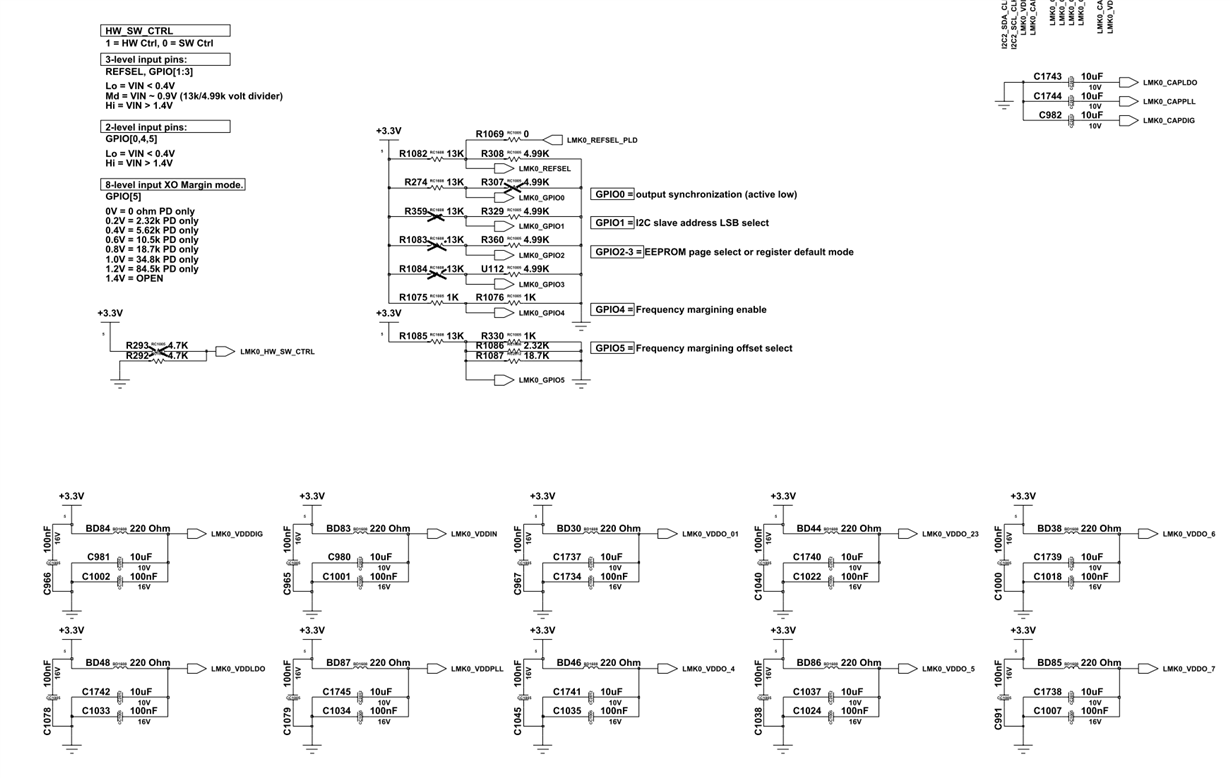

-当附加文件处于设置值状态时,请按如下所示更改寄存器:

将 R59保持在0x42、并将 R56 (PLL_POST_DI费)更改为0x0a、R33 (OUTPUT DIV)、R36、R38、R40、 R42、R44至0x0a => 156.25MHz

您能否查看附加文件中的设置以了解问题?

提前感谢您的帮助

e2e.ti.com/.../HexRegisterValues_2D00_20191015_5F00_2_5F00_Clkoutput_5F00_OK.txt

谢谢你

Mark Kim