请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMC555 您好!

感谢您的支持。

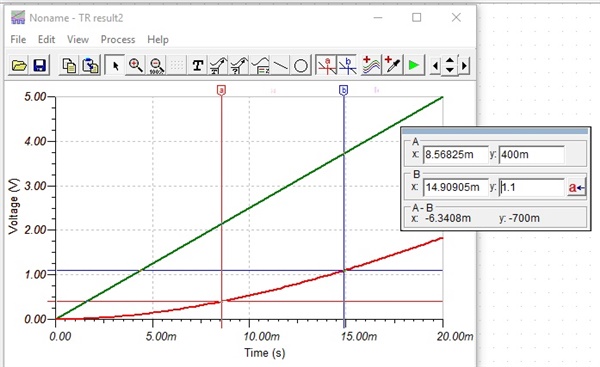

在上电时、尤其是长时间放电后、输出引脚在没有触发至 Q1的情况下在以下电路上变为高电平。 什么是根本原因?

为了避免这种情况、我们正在考虑停止将 RESET 引脚直接连接到 Vcc、将以下 RC 电路插入 RESET 引脚、并在电源开启时应用 RESET。 请告知我们 C 和 R 的建议值。Vcc 的上电时间大约为20ms。

请告诉我们..

谢谢、此致、

M.Hattori。