请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2582 你好

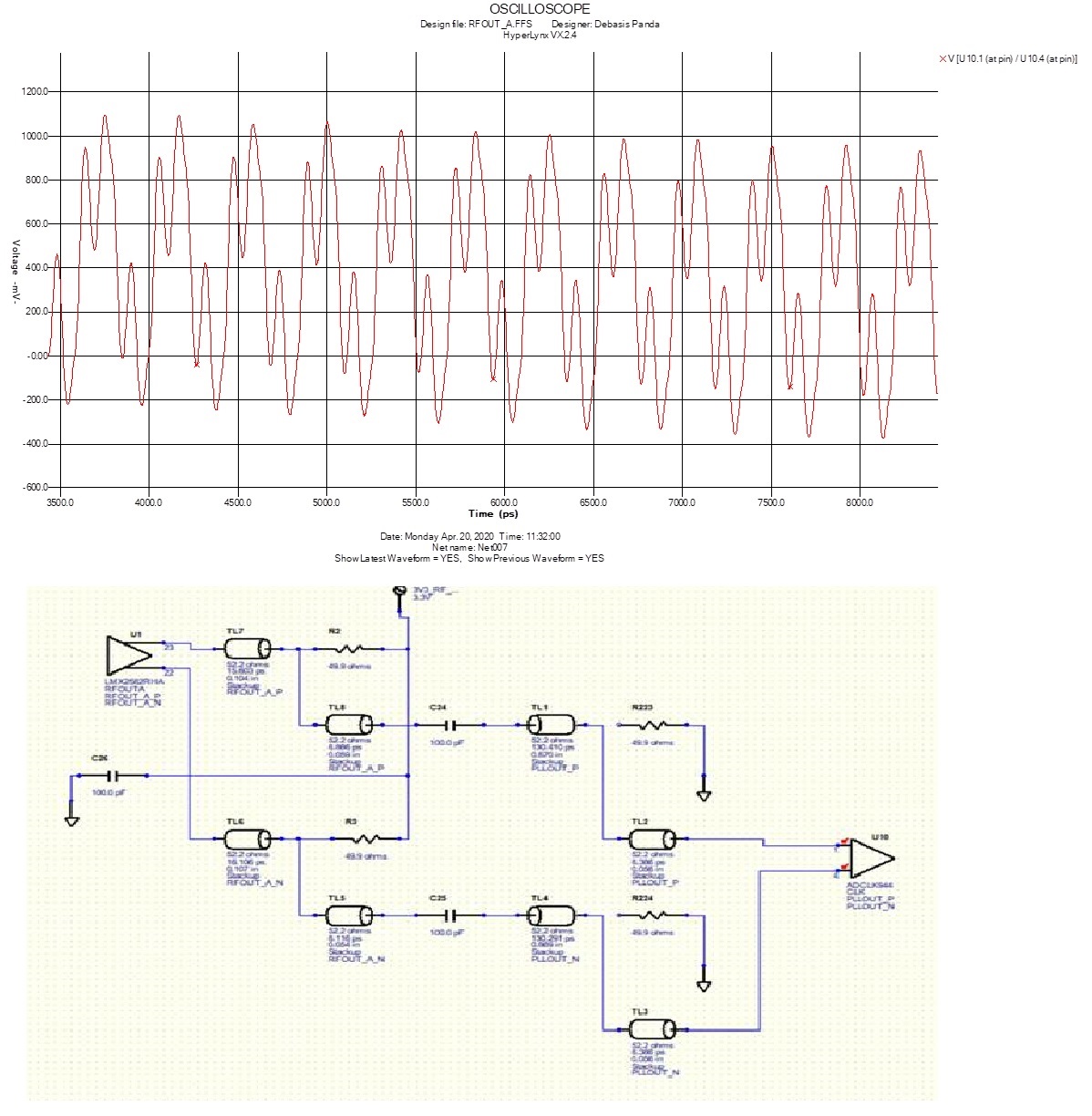

在我的设计中、LMX2582时钟合成器从 Analog Devices 连接到 ADCLK944器件。 LMX2582的输出配置为差分时钟模式、 PCB 上的差分阻抗 为100欧姆。 所有电路均符合 LMX2582的参考设计。

我正在使用 Hyperlynx SI 分析工具检查 ADCLK944的后置布局时钟质量。 时钟质量非常差。 也通过隔离 ADCLK944器件进行了尝试、但结果没有改善。

LMX2582在原理图设计与参考设计相同且使用 TI 网站上提供的 IBIS 模型时、哪些因素可能会导致 LMX2582无法生成合适的时钟、事件? 因为我即将发布设计、所以需要快速帮助。

此致