主题中讨论的其他器件:TIDA-010122、 PLLATINUMSIM-SW

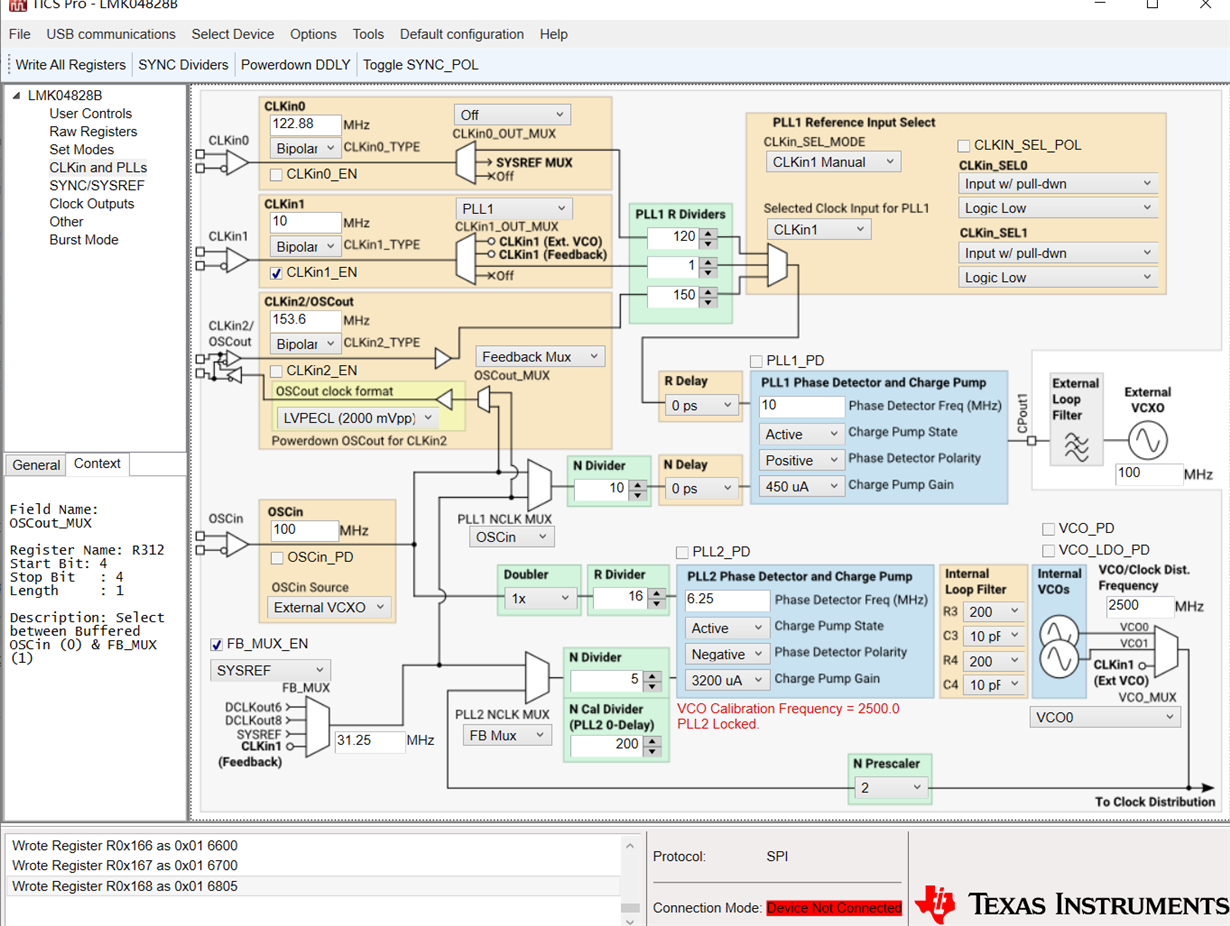

LMK04828B 配置如下:

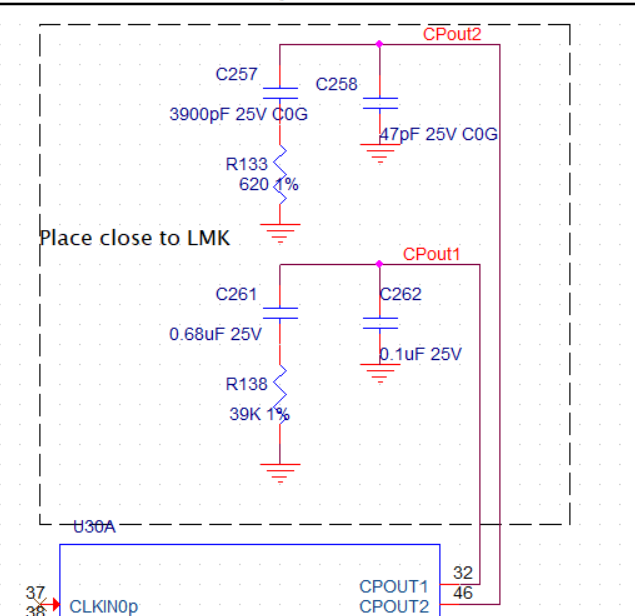

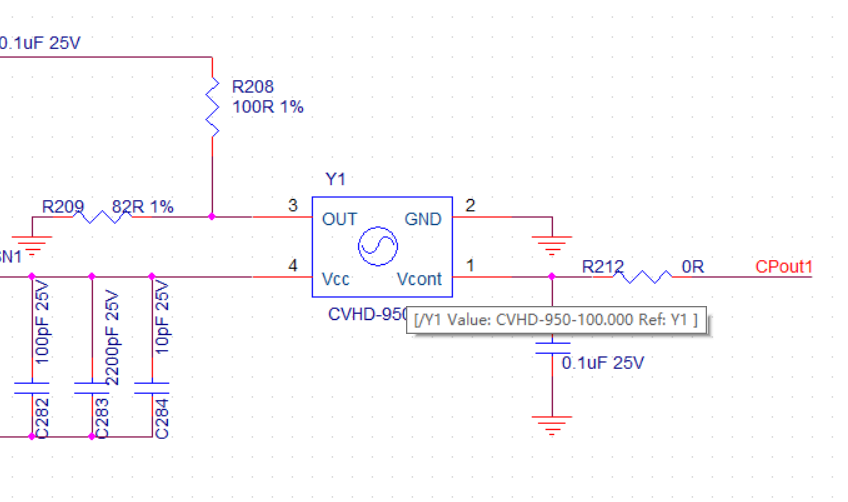

硬件设计请参阅 TIDA-010122

10MHz 输入 Clkin1、双 PLL 模式、输出频率:31.25MHz、125MHz、250MHz

反馈多路复用器= SYSREF = 31.25MHz

我们制造多达15个板。 其中大多数(并非所有)都有以下现象:

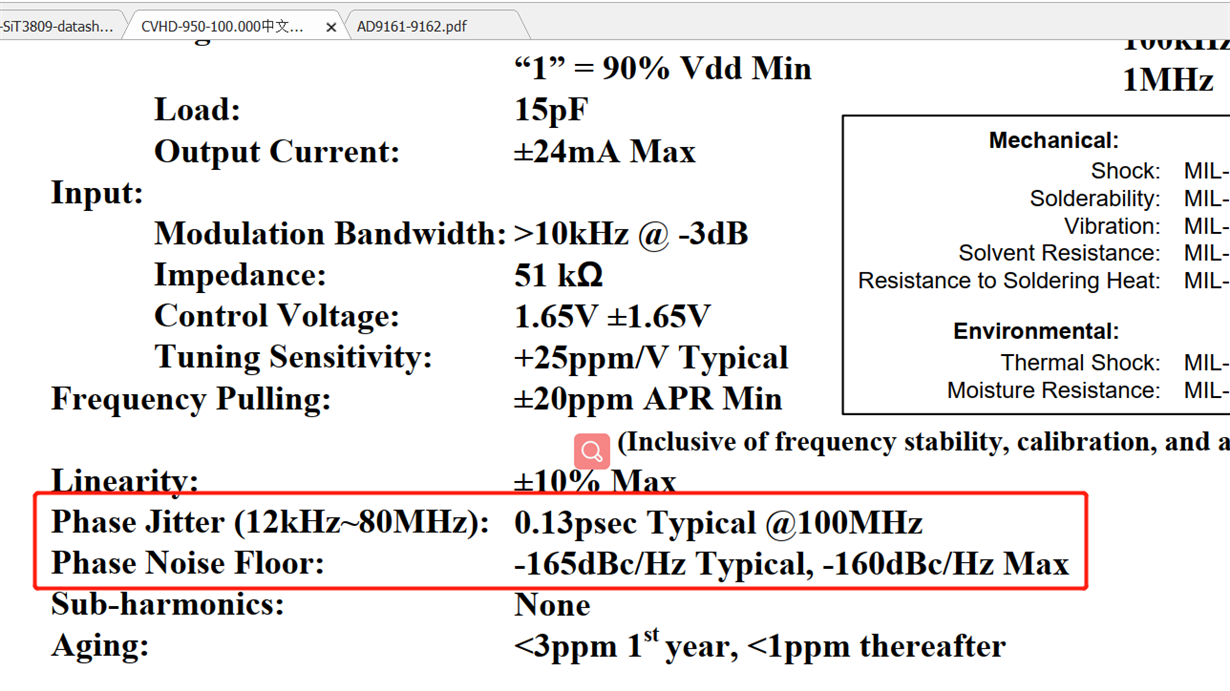

为这些板加电后、我们使用一个小风扇来冷却它们、PLL1和 PLL2的锁定检测 LED 将打开并保持不变。 但是、当我们尝试使用功能更强大的风扇来冷却它们时(重点关注 LMK04828B)、PLL1的锁定检测 LED 将闪烁、而 PLL2锁定 LED 不会闪烁。 然后我们更改为小风扇、PLL1锁定 LED 将逐渐保持灯亮。

所有这些电路板都浸没在3M 的电子氟化液体中。

显然、温度会影响 PLL1锁定。 有人可以给我一些帮助吗? 谢谢!