请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04832 为了分析双环路模式下 LMK04832的总体相位噪声性能、我首先分析 PLL1、然后导出布线、然后在分析 PLL2时将该布线用作源。 我的问题是有关 PLL1的分析。

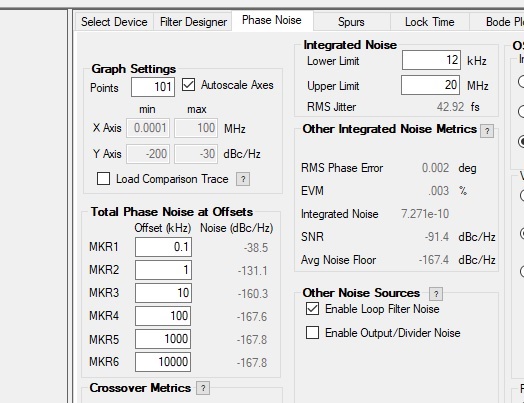

1.在分析 PLL1时、如果打算将其用作 PLL2的输入、而在计划将 PLL1的 VCXO 频率用作 PLL2的输入频率时、是否取消选中其他噪声源下的"启用输出/分频器噪声"?

谢谢