- 数据表中的 PWM 示例是如何工作的?

- 数据表 PWM 示例有哪些限制?

- 是否有方法可以提高线性度和占空比范围?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

此常见问题解答涵盖了 PWM 电路。 下面的图1显示了使用 LM555、 NA555、 NE555、 SA555 和 SE555 计时器的脉宽调制器、分别称为 LM、NA、NE、SA 和 SE。 由于其设计、它们被称为双极计时器。 本常见问题解答还涵盖 了 LMC555和 TLC555计时器、这些计时器在下文中分别称为 LMC 和 TLC。 作为一个小组、由于其设计、它们被称为 CMOS 计时器。 此常见问题 解答也适用于 xx556、TLC551和 TLC552计时器。 定时器的电源电压引脚使用不同的符号、即 VS、VCC 和 VDD、它们具有相同的功能。

数据表示例电路

数据表显示了使用555计时器实现 PWM 的设置:

图1中的电路是单稳脉冲发生器,可提供理想的输出高电平时间-ra*C*ln (1-VCONT/VDD)。 输出频率将与时钟输入频率 FI 非常匹配。 产生的输出占空比为–RA*C*ln (1-VCONT/VDD)/FI。 因此、输出占空比以非线性方式随 VCONT 而变化。 非线性是计时电容器斜坡为指数曲线的结果。 占空比也随 RA、C 和 FI 而变化。

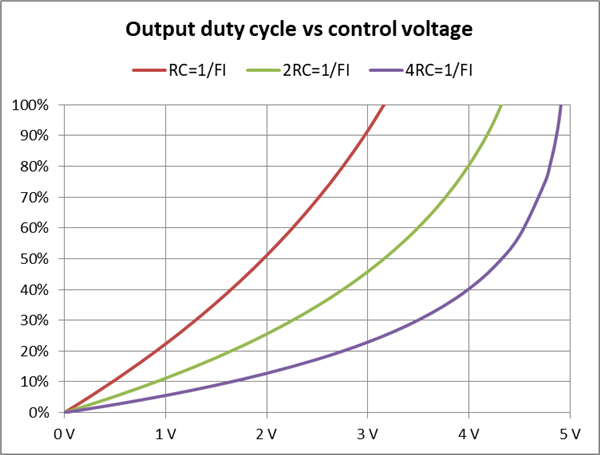

数据表示例使用 RA = 3kΩ μ F 和 C = 20nF 的值、将 RC 时间常量值 RA*C 设置为60µs μ F。 该示例提到,RA*C 乘积设置为时钟周期除以4。 换言之,240µs 周期是 RA*C 乘积的4倍。 此设置的控制电压到占空比传递函数可在图2的4RC = 1/Fi 图中看到。 显然、线性度非常差。 接近输入时钟周期的 RA*C 值(例如 RC =1/Fi 和2RC =1/Fi)的结果更加线性。 请注意、增加 RC 乘积也会压缩控制电压范围。 图2显示了相对于输入时钟周期的不同 RC 时间常数的理想传递函数。

图2. 每个计时周期内各种 R*C 产品的占空比与控制电压间的关系、1/FI。 VDD=5V

在使用555计时器设计 PWM 信号时、需要考虑其他限制因素。 例如、驱动触发输入的外部时钟必须具有一个低负占空比、输出低电平时间百分比、这是因为 PWM 输出最短高电平时间不能小于输入时钟低电平时间。 在 A 稳 态设置中、可以使用另一个555计时器生成外部时钟。 低于10%或接近100%占空比的运行会导致额外或缺失的输出脉冲。 在后一种情况下、占空比和输出频率下降一半。 LMC 的最小有效控制电压为0.4V、TLC 的最小值为0.5V。 在较低的控制电压下运行将导致占空比固定、或者可能导致不一致的脉冲流。

双极定时器的存储延迟约为16µs μ s、这会限制最小占空比。 这些器件的最大占空比限制为约97%。 调整控制电压以尝试更高的占空比将产生具有分频的输出。 在这种情况下、由于缺少输出低电平脉冲、频率被分频、从而导致占空比接近50%。 当输入电压接近 VDD 时、双极定时器也会增加阈值电流。 该输入偏置电流可限制高占空比最大值。 添加 RL 可以提高双极定时器的 VOH 电平、但它们中的任何一个都不需要。

使用数据表中的 RA = 3k 和 C = 20nF 示例、时钟周期为60µs μ s、120µs μ s、240µs 产生表1中的最小占空比和表2中的最大占空比。

|

周期 |

不适用 |

SE |

Lm |

LMC |

TLC |

|

60µs μ A |

26 % |

25% |

24 % |

12% |

16% |

|

120µs μ A |

13% |

14% |

12% |

6% |

8% |

|

240µs μ A |

7% |

7% |

6% |

3% |

4 % |

|

限制器 |

16美制 |

16美制 |

15美制 |

0.4V |

0.5V |

表1:最小占空比 RA=3k、C=20nF

最小占空比受双极定时器的16µs μ s 延迟和 CMOS 定时器的控制电压最小值的限制。

|

周期 |

不适用 |

SE |

Lm |

LMC |

TLC |

|

60µs μ A |

97% |

95% |

98% |

98% |

98% |

|

120µs μ A |

98% |

98% |

98% |

98% |

98% |

|

240µs μ A |

98% |

85% |

95% |

97% |

98% |

表2:最小占空比 RA=3k、C=20nF

最大占空比受脉冲跳跃的发生以及双极定时器上的输入电流的限制。

总之、数据表脉宽调制器示例非常适合抗线性不良且无需在接近0%或100%占空比的情况下运行的应用。

改进的示例电路

图3是一个改进了很多、但仍然不完善的 PWM 发生器。 它使用50%固定占空比555计时器振荡器和比较器。 A 稳态振荡器常见问题 解答描述了如何使占空比为50%的振荡器。 也可以使用这些公式来选择组件。 Rb * C = 0.481/F、RA = Rb / 2、RD = 0.15 * RA、其中 F 是振荡器频率。 比较器执行直流输入电压至输出 PWM 占空比转换。 计时电容器的充电和放电呈指数斜坡。 但是、转换时使用上升斜坡和下降斜坡。 因此、大部分非线性会被消除。 在输出频率可被分频的条件下、这个电路可在低至0%和高达100%的范围内使用。 但是、占空比是正确的、而不是图1原理图中会出现的50%。 R1、R2和 R3将输入电压调节到1/3至2/3 VDD 之间、以匹配计时斜坡电压范围。 LM293需要至少6V 的 VDD 才能将斜坡电压保持在输入共模范围内。

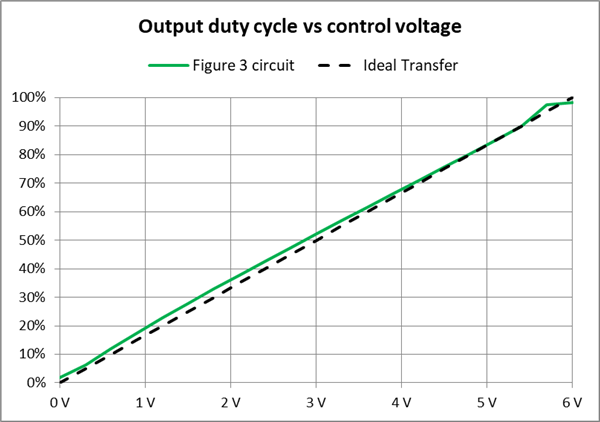

图3原理图的示例实验室结果如图4所示。 虚线表示理想的线性传递函数。 可以看出、该电路的输出占空比比比比比图1中电路的结果更加线性。

图4. 使用电路图3、VDD = 6V、C = 1nf 时、PWM 占空比与控制电压间的关系。

传递函数结果类似于理想的传递函数曲线。