主题中讨论的其他器件: LMK04832、 LMK04616、 ADC-WB-BB、 LMK00804BEVM、 LMK1C1104、 LMK00804B

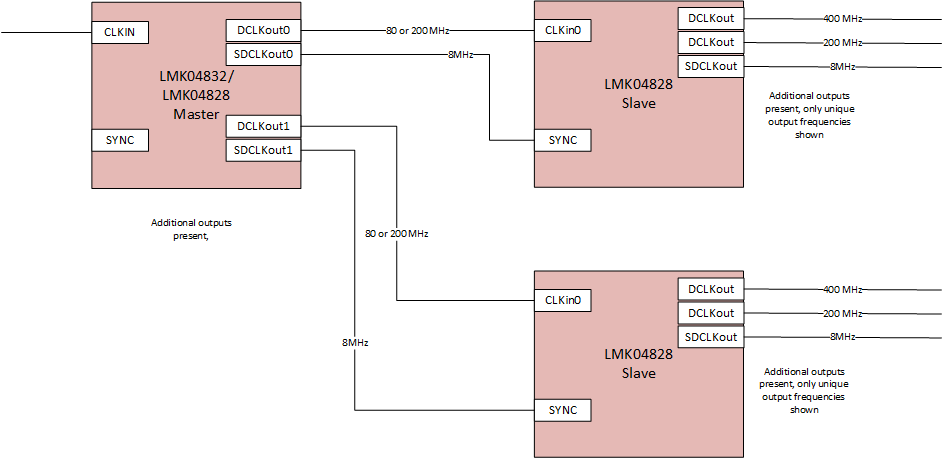

在最近的一篇文章中、我正在寻求帮助、以确定几个不同的器 件(LMK04832、LMK04828和 LMK04616)用作驱动两个(最终为4个)从器件 LMK04828的主器件。 Derek 与 TI 一起出色地传达了每个人的特点。 随着该帖子的发布时间越来越长、我想创建一个单独的帖子、以讨论主器件的输出驱动配置。 下面简单的背景方框图、后跟问题:

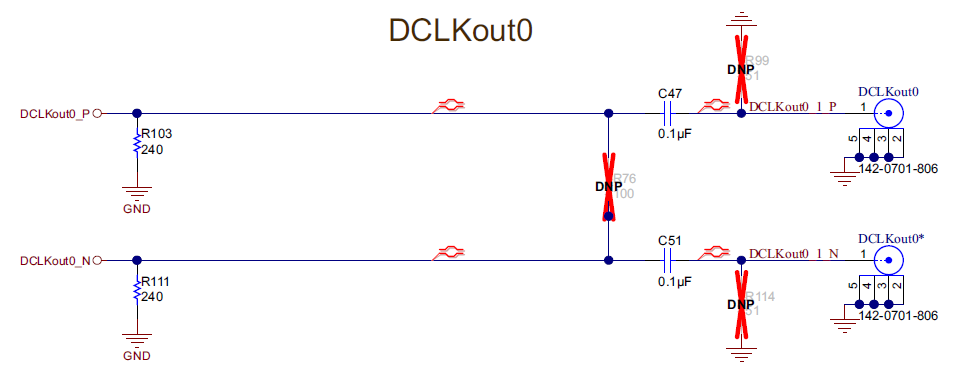

由于现有的电路板限制、主器件必须通过一个到从电路板的单端输入来驱动从器件、此输入为 AC 耦合、此输入在到达从器件 LMK04828基准输入之前经过3dB 衰减器。 这意味着任何不涉及额外电路或平衡-非平衡变压器的差分驱动都需要在主板上端接。 驱动至从器件单端输入的频率可以是80MHz 或200MHz。 此外、对于我们的初始试验、主板将托管在现有的 TI 开发板之一上。 回答我的问题时、请考虑以下几点:

对于作为主器件的 LMK04832、这确实是最合适的情况、我计划使用 LVCMOS 输出配置来驱动从器件 LMK04828、这需要对开发板输出终端进行极小的更改。 在上述限制条件下、这似乎是最佳选择吗?

2.对于使用第3个 LMK4828作为主器件的次要情况、Derek 提醒我、只有 OSCOUT 支持 LVCMOS。 Derek 提到在 LMK04828上使用 LVPECL (在另一次对话的背景下) 来驱动从器件 LMK04828的交流耦合单端基准输入。 我想与 Derek 或其他人确认、考虑到我们在终止选项方面存在的限制、这是否确实是最佳选择。

谢谢