请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2594 我刚刚开始了一些非常简单的 LMX2594 PLL 仿真。 我不断发现引用的环路带宽与波特图不匹配、并且超出了一个数量级。

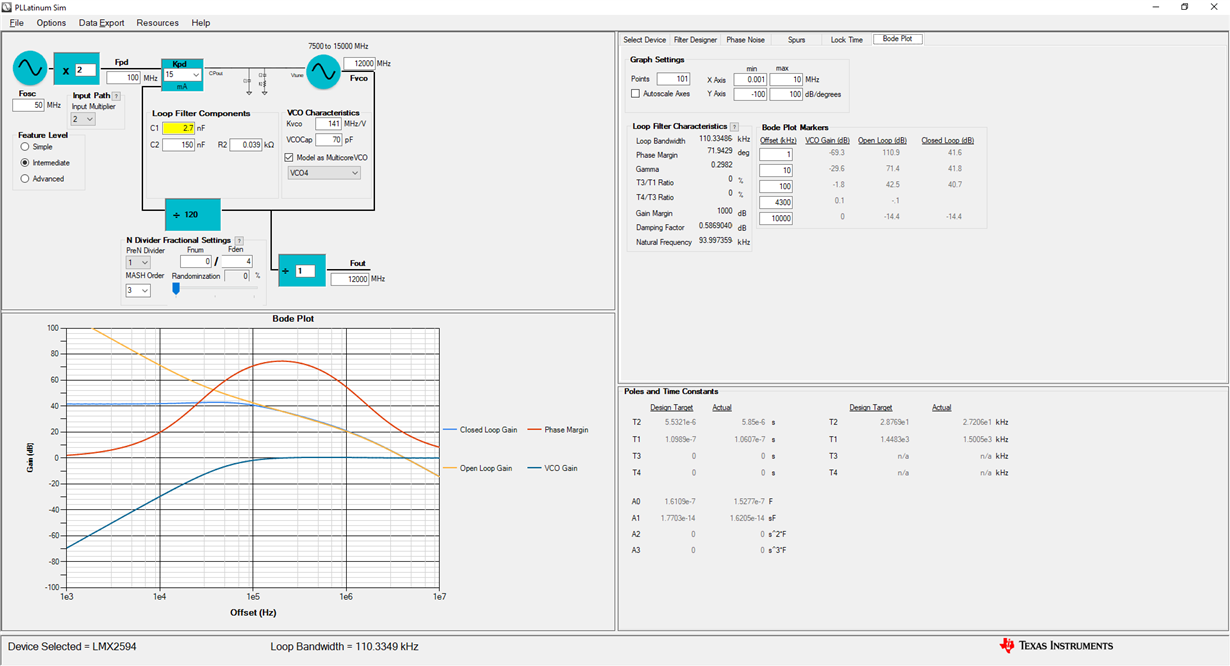

我指定了100kHz 的环路带宽和70Deg 的相位裕度。 单击计算环路滤波器、没有像 VCOCap/MinHighCap 限制带宽这样的错误、 出现新的滤波器值、相位噪声发生变化。 底部的总结具有实际环路带宽-指定了110kHz 与100kHz、但计算调整为 R 和 C 的实际值、因此该误差看起来是合理的。

波特图窗口在图表和标记数据中显示了明显不同的增益。 0dB 点可能为4.3MHz。 在110kHz 时、相位裕度达到~70deg -因此看起来是正确的。 计算出的波特增益可能比预期高30dB。

我也尝试过三阶和四阶场景、遇到了相同的问题。

下面是波特图窗口的屏幕截图。

此致 David