Other Parts Discussed in Thread: DAC38J84, LMK04828

主题中讨论的其他器件:DAC38J84、

大家好、

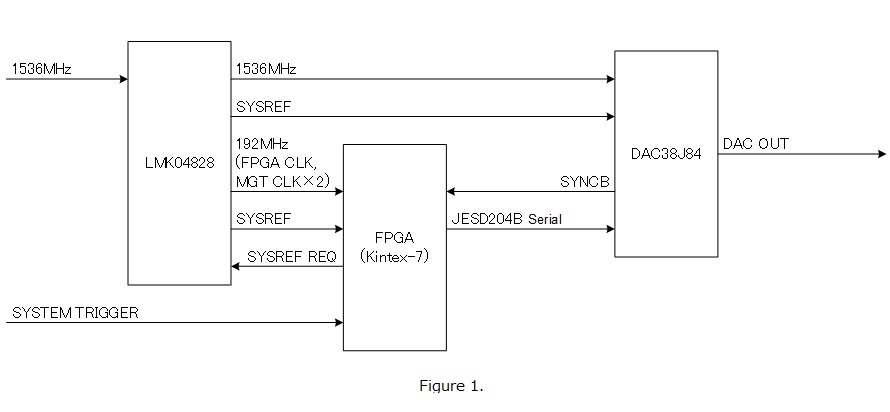

我们目前使用 Xilinx FPGA Kintex-7和 Xilinx JESD204 IP 内核通过 TI DAC (DAC38J84)输出模拟信号。

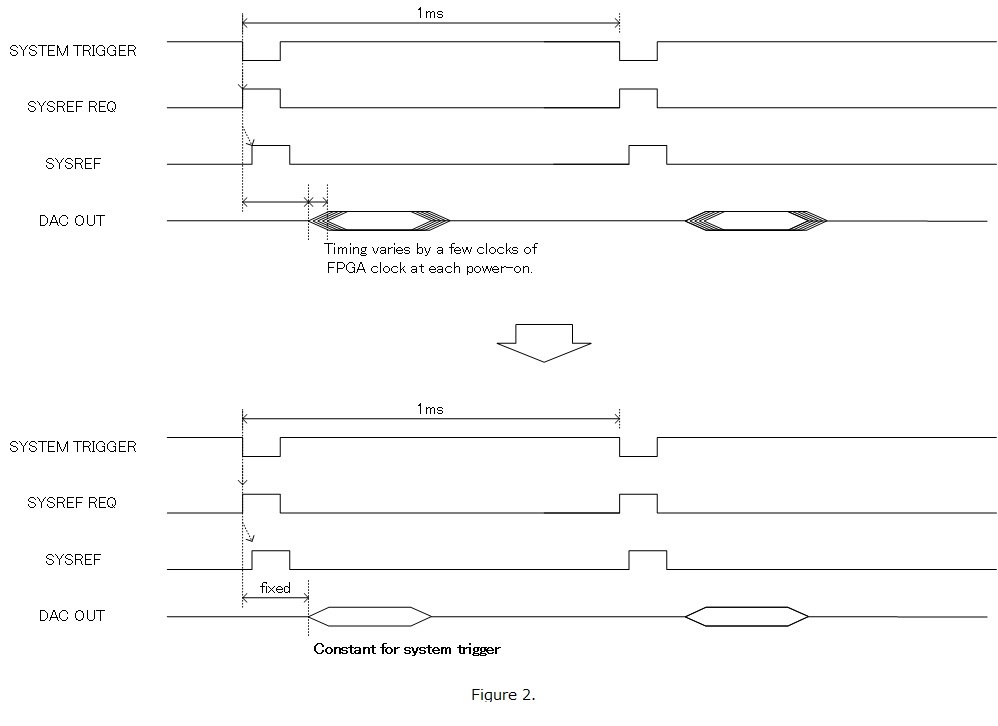

例如、FPGA 每1ms 接收一次触发信号、并且需要在该时间输出模拟信号、但每次打开电源时、FPGA 时钟中的几个时钟之间的模拟输出时序会波动。

但是、模拟输出时序在每次电源启动时的几个时钟之间变化、我们希望在相同的时序输出模拟信号。

我们在子类1中使用 JESD204B、但我们在子类1方面没有太多经验、也不了解 JESD204B 的操作、因此我们想向您询问以下内容

"运行条件"

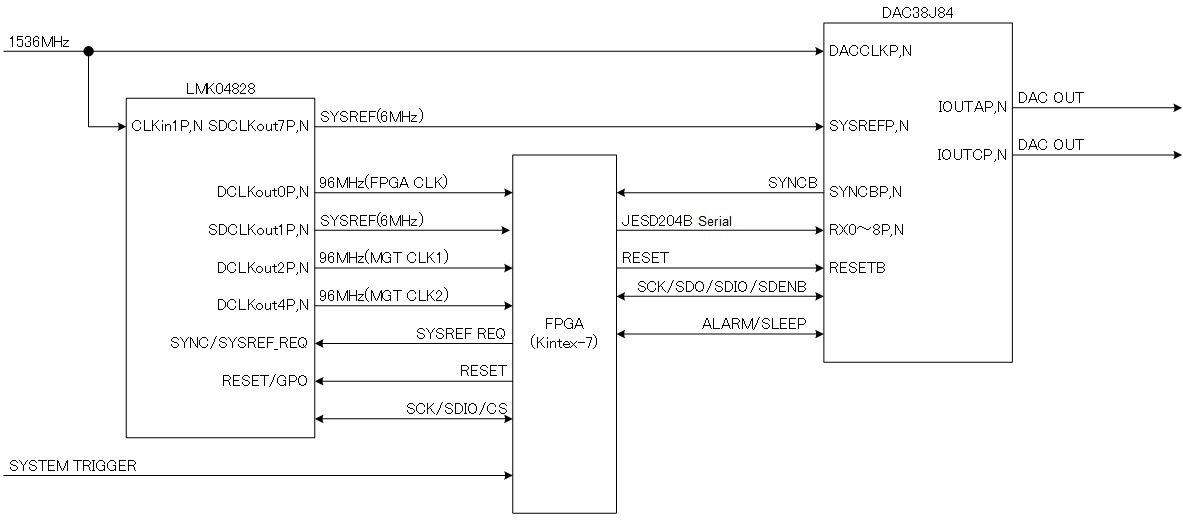

DAC 为 DAC38J84、LMK04828用于时钟和 SYSREF 生成。

LMK04828 CLKin1/FIN/FBCLKIN (引脚34、35)、其中 LMK04828具有1536MHz 输入、DAC 具有1536MHz 输入、1536MHz 除以1536MHz、FPGA 具有192MHz 输入、DAC 和 FPGA 具有 SYSREF (8MHz)(由脉冲发生器提供给 DAC 和 FPGA)。 (图1)

FPGA 是一款具有 JESD204子类1 IP 内核的 Xilinx Kintex-7。

"问题"

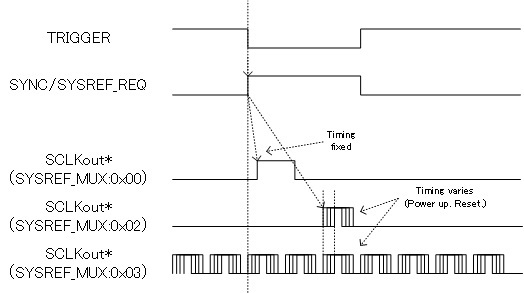

Q1)是否可以将 SYSREF 的相位调整为与1ms 同步的触发时序、如图2所示?

简而言之、我想将触发器用作 SYSREF_REQ 信号并使其具有相同的时序(相同的延迟)。

触发时序与时钟同步、但与 SYSREF 的相位关系每次都会变化、因为每次启动时的时序都不同。

但是、由于时序与整个系统同步、因此启动后的相位关系是恒定的。 触发器和 SYSREF 的时序不变。

Q2)我对 DAC 的运行有疑问。

例如、如果寄存器固定为特定设置、DAC 中的内部延迟是恒定的还是波动的?

例如、DAC 中特定寄存器设置的内部延迟是恒定的、还是存在变化的因素?

它可能与 FPGA 的 IP 内核有关、但我想知道是否可以在每次启动时输出模拟信号而不会出现任何触发时序波动。

Q3)我对 DAC 的运行有疑问。

DAC 的同步信号输出与 DAC 模拟信号输出之间的关系(延迟)是否恒定?

我认为 FPGA 和 DAC 之间的时序只能通过来自 DAC 的 SYNC 信号来确定、但我认为如果 SYNC 和 DAC 模拟信号输出之间的关系不同、则可能很难使时序保持恒定。

如果您还有其他需要注意的问题(设置、使用等)、如果您能给我一些建议、我将不胜感激。

此致、

T.Karita