大家好、

由于 数据表或任何应用手册中未提供 LMK04616的 SYSREF 计时、因此我希望获得一些帮助、以了解我们的客户对该 SYSREF 计时的询问:

以下是客户问题的内容:

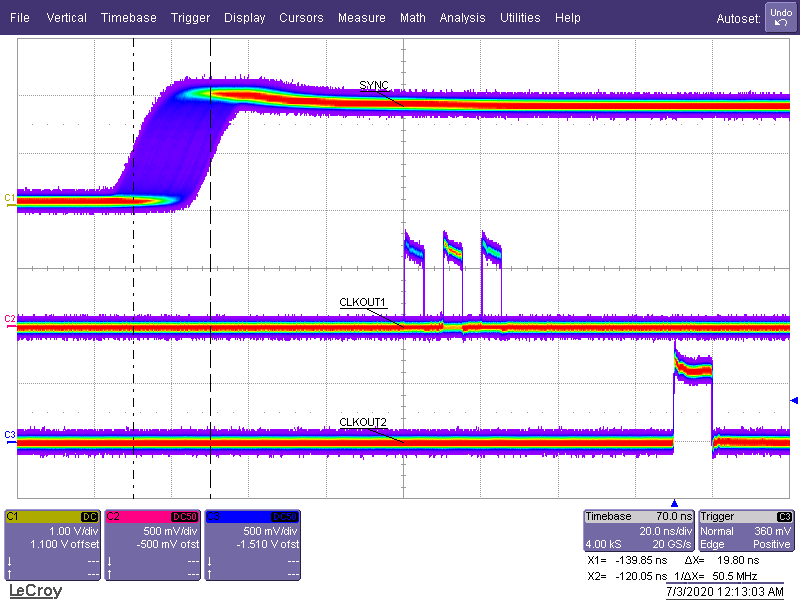

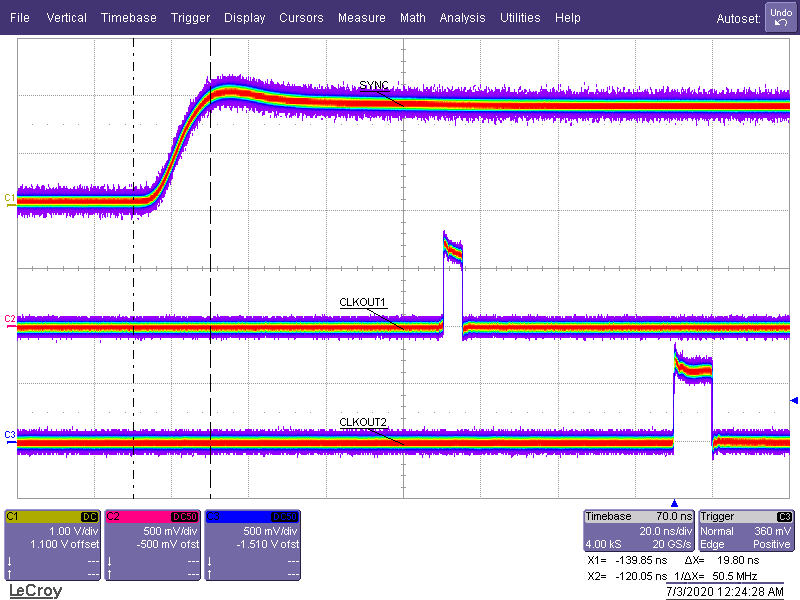

假设16位分频器用于将 CLKout 设置为100MHz。

当使用通道作为 SYSREF 时:

当 sysref 脉冲计数器为1时、SYSREF 持续时间是多少? 10NSec 的逻辑高电平

外部 SYNC 和 SESREF 输出之间的持续时间是多少?

3.它是确定性的时间吗?

4、如果时间不是确定性的、我可以通过在外部 SYNC 引脚上使用一些逻辑来使它具有确定性吗?

假设一个通道使用100MHz、另一个通道使用50MHz (同步)。

1.我可以计算 CLKout1处从外部同步到 SYSREF 的时间、CLKout2处的 SYSREF 时间吗?

2. CLKout1和 CLKout2之间的时间是否在每个 SYSREF 请求的持续时间相同?

3.如果答案是否定的、我可以通过在外部 SYNC 引脚上使用一些逻辑来确定它吗?

如果您对客户有任何疑问、请告诉我。

谢谢!

Jonathan