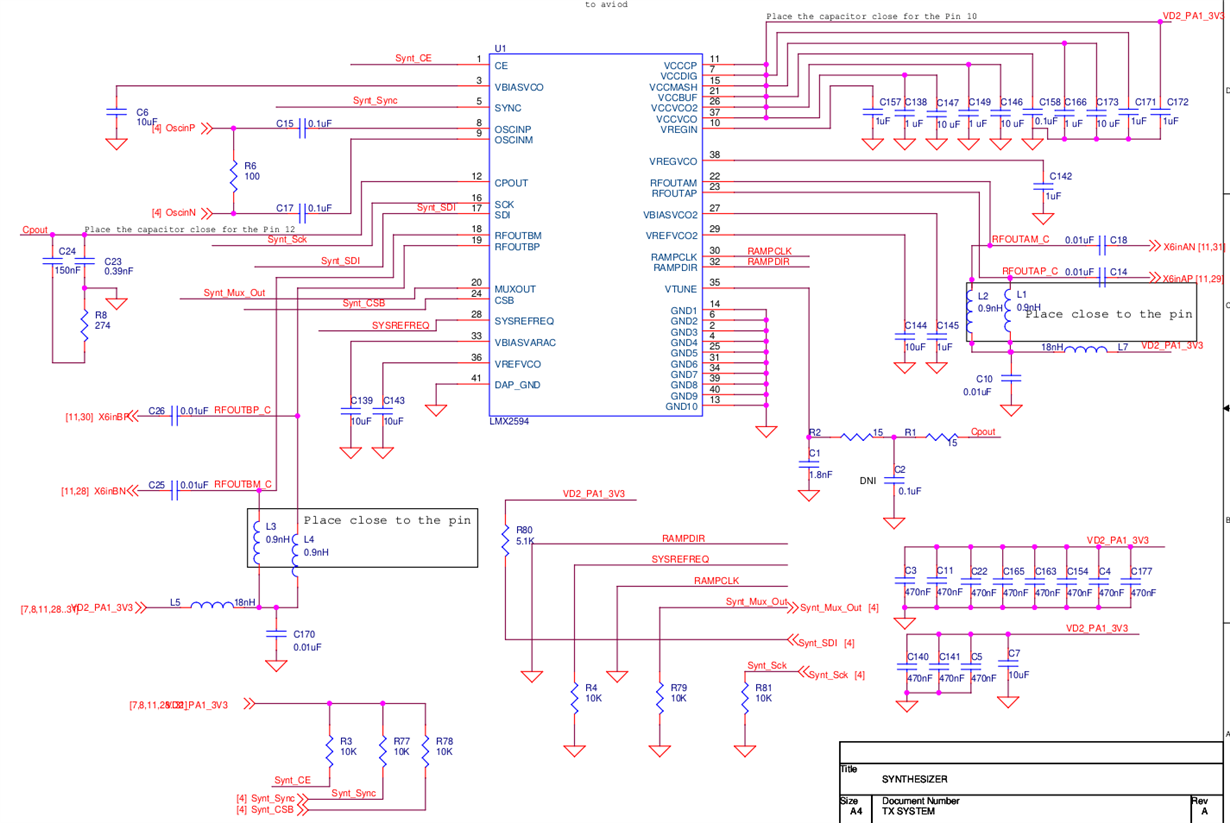

我们设计了一个收发器系统、其中 LO 由 LMX2594在12.5GHz 输出下生成。 我已使用 PLLatinum 仿真工具来设计环路滤波器。 滤波器最初设计用于20.833MHz Fosc。 输入参考时钟由模拟器件的 HMC7044提供。 我们的设计要求将 Fosc 限制为2.604MHz 至100MHz 的整数倍、例如10.433MHz、20.833MHz、41.667MHz 等 原理图附在下面-

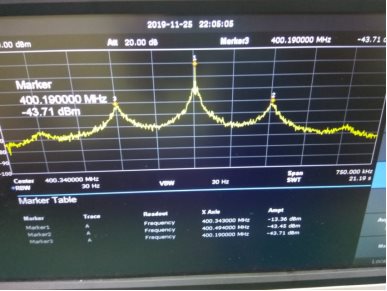

但是、在实际硬件中、性能不如预期好。 有2种类型的杂散:1)载波的偏移约为3kHz、2)载波的偏移约为150kHz。 性能的折衷如下所示-

将 Fosc 降至 2.604MHz 可改善150kHz 的偏移杂散、但会降低3kHz 的偏移杂散

2.将 Fosc 增加到41.667可改善3kHz 偏移杂散、但会降低150kHz 偏移杂散。

下面是在 Fosc=20.833MHz 且启用 OSC_2X 的情况下我所指的150kHz 杂散(频率已由我们的 Rx 进行降频转换以适应频谱分析仪范围)-

1.您能否建议一些方法来改善 Fout 相位噪声和性能、例如更好的滤波器和原理图设计或 LMX2594配置中的任何其他设置?

2.在 FPD 和电荷泵电流之前、OSC_2X 倍压器有多大的效率来改善 PN?

Fout 也会随着时间的推移偏离其初始锁定频率。 原因是什么?如何改进?

谢谢

Samarth