我遇到与此主题相同的问题: e2e.ti.com/.../833011

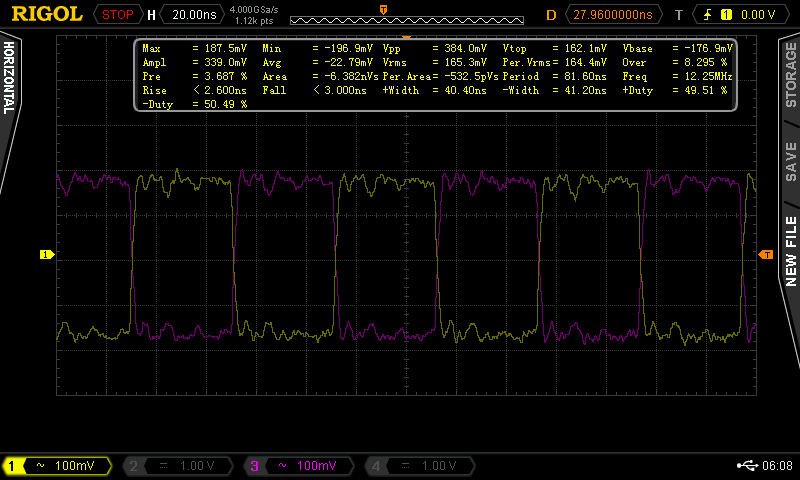

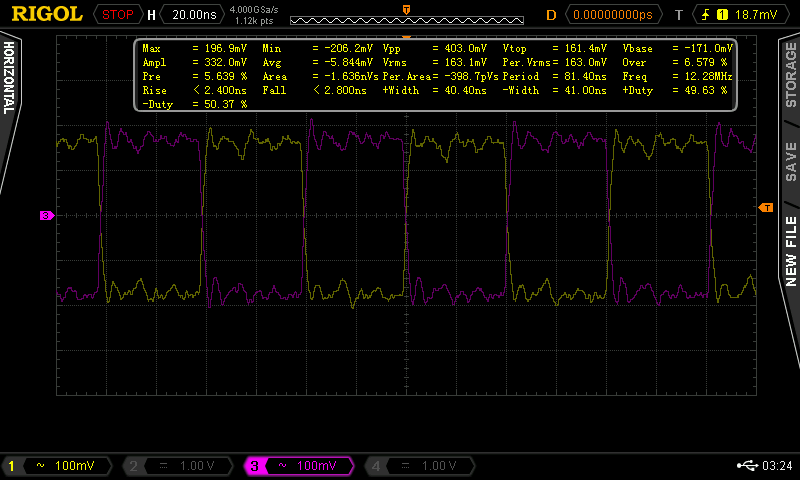

这个线程上的人显示了使用 LMK04832的市售电路板的原理图;我使用的是同一电路板、但显然是更新版本、在 OSCin_N 和接地之间添加了0.1uF 电容器)。 我也无法使 PLL1锁定在双环路模式、 并已确认只有 PLL1未锁定(PLL2锁定到 PLL1的输出、即使 PLL1未锁定、因为由于 VCXO 的调谐范围有限、它仍接近预期频率)。 我还通过尝试环路极性并观察示波器上的 VCXO 调谐电压来确认这一点。 正如预期的那样、根据环路极性、它的轨输出为3.3V 或0.0V。 您还有其他提示来让 PLL1锁定吗? 我使用的是450uA CP 增益、但由于 PLL1环路滤波器的环路带宽如此低(它具有0.1uF + 0.68uF 环路滤波电容器)、我不认为这可能是稳定性/相位裕度问题。 我已附上 TCS 文件的当前草稿。