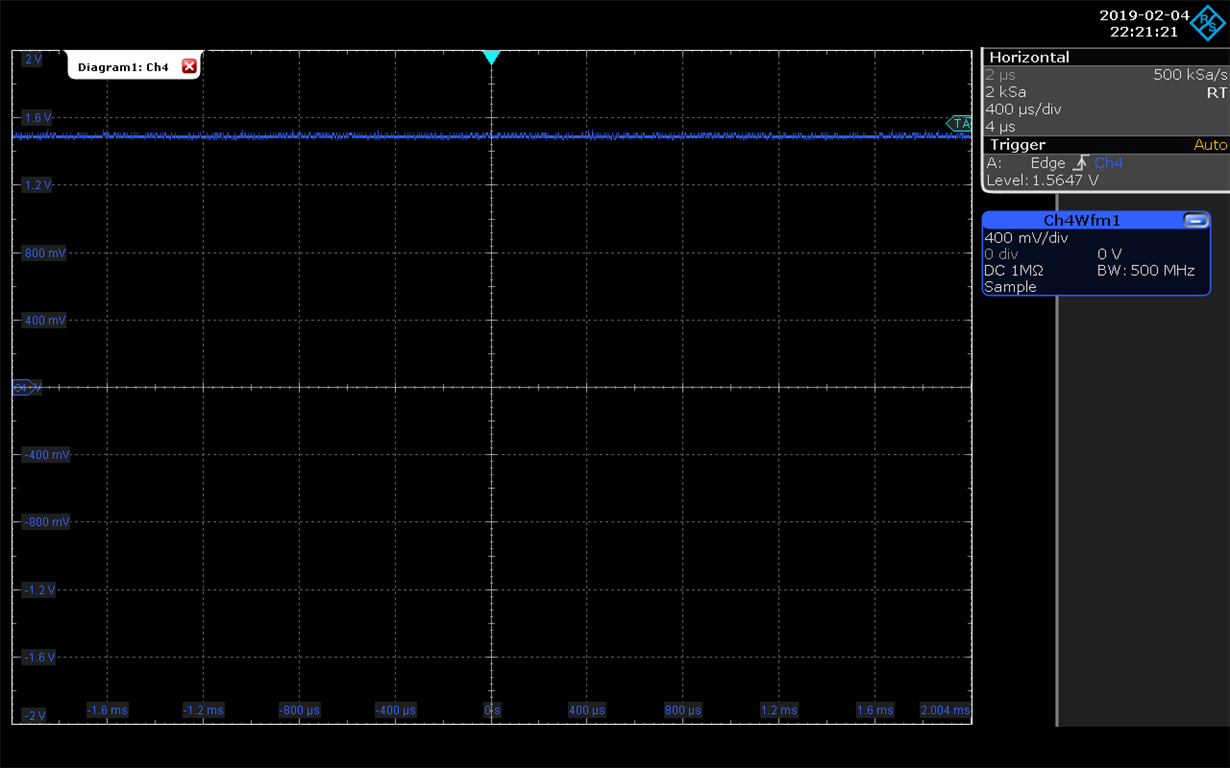

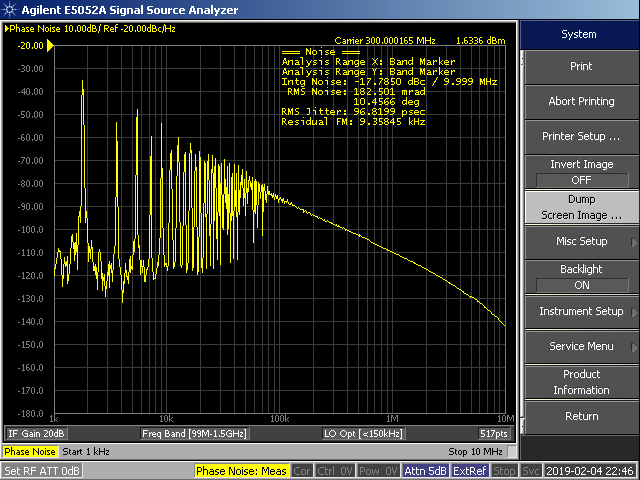

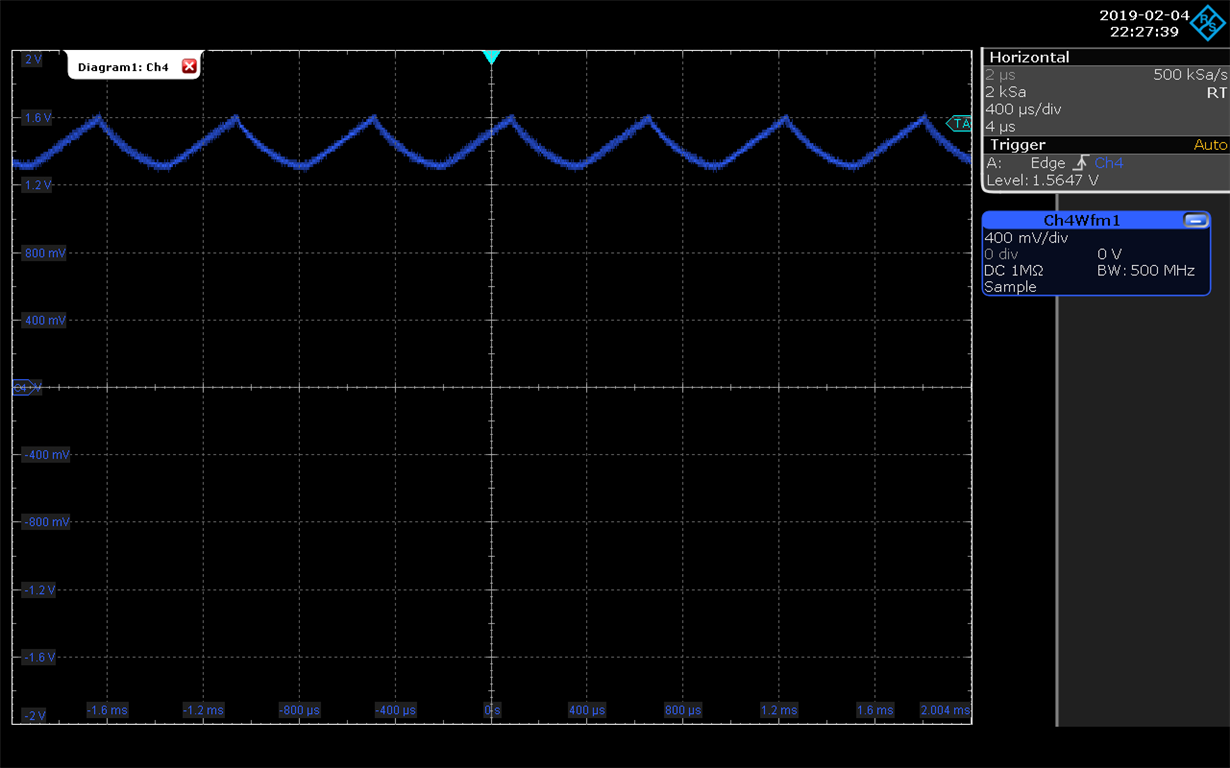

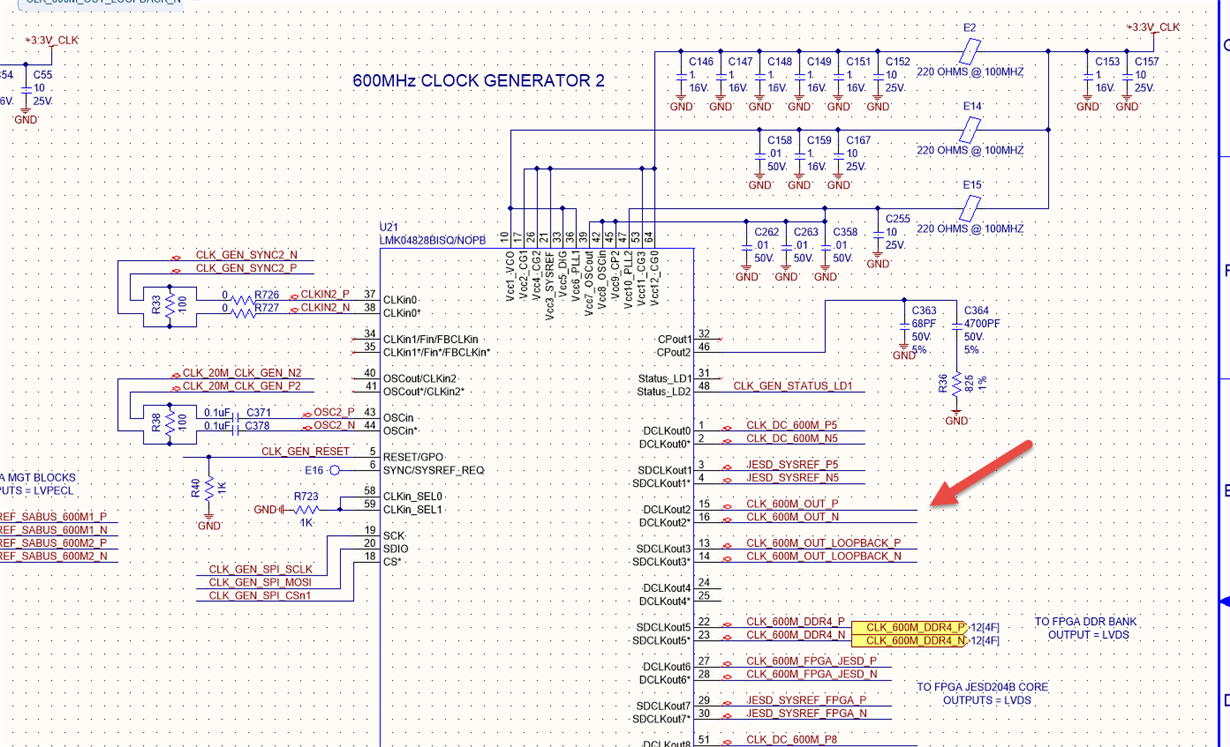

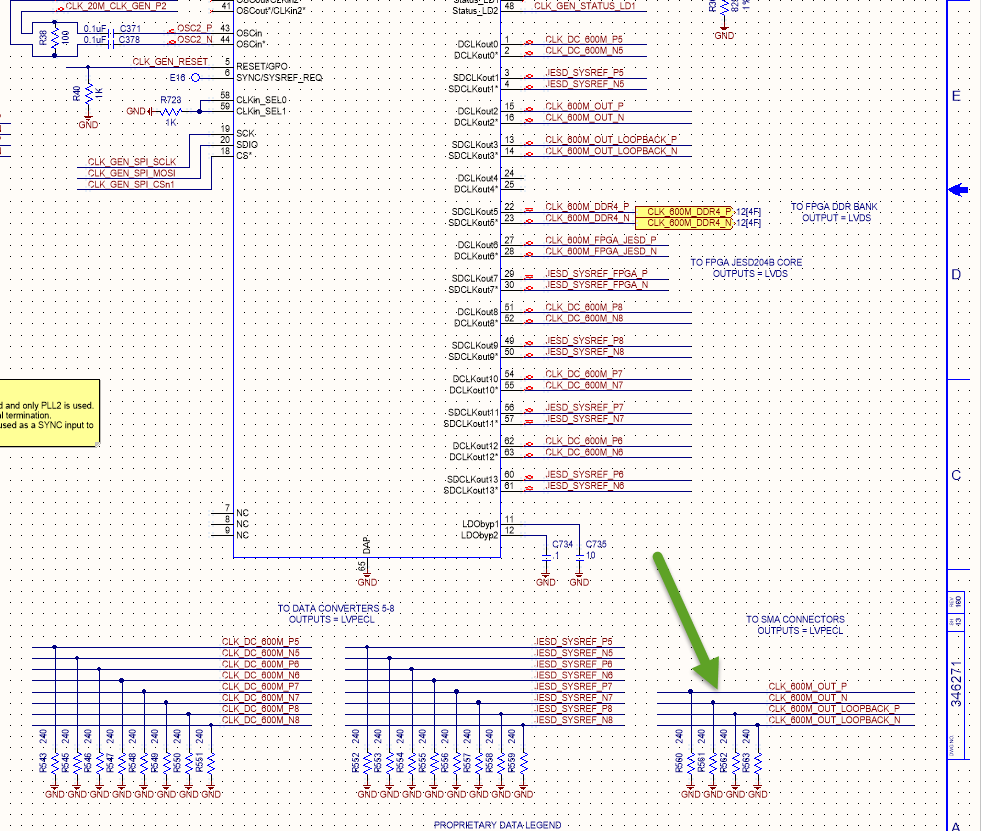

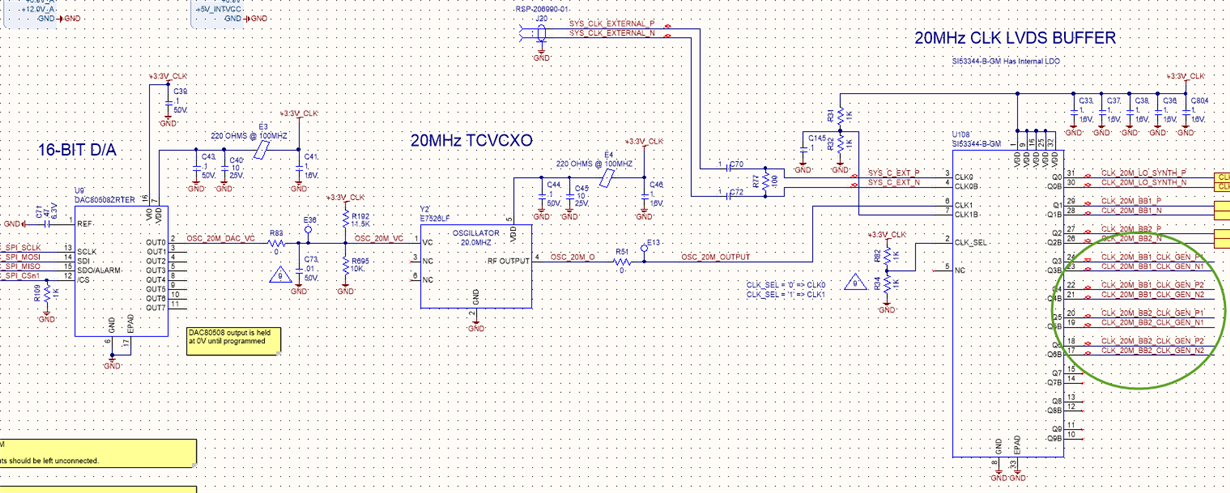

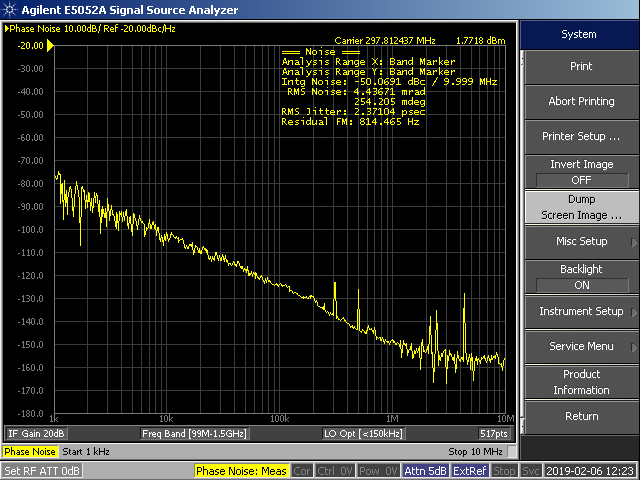

我们有一个包含两个 FPGA 和四个 LMK04828的电路板。 每个 FPGA 对两个 LMK04828进行编程。 但是、四个 LMK04828中的每一个都共享相同的振荡器基准、该基准使用低抖动 LVDS 缓冲器扇出。 与使用评估板获取的基线相比、第一个 FPGA 编程的两个 LMK04828似乎具有可接受的相位噪声性能。 但是 、连接到第二个 FPGA 的其他两个 LMK04828在100k 偏移下具有可怕的相位噪声、并且电荷泵输出引脚似乎具有类似锯齿的波形。 前两 个 LMK04828在原理图设计中与第二组 LMK04828相同、它们的布局非常相似、但并非100%相同。 我不明白第二组连接到 FPGA 2可能会发生什么情况。 它们在所有电路板上都是这样、因此它不仅仅是一个一次性问题。 我将介绍评估板基线的屏幕截图、该基线具有大约287fs 的抖动、第一个 FPGA 上第二个 LMK04828之一的输出及其 CPout 值、 第二个 FPGA 上第二个 LMK04828的输出及其 CPout 值。 还包括原理图部分的屏幕截图、其中显示了用于连接到 E5052A 的输出。 由于输出为 LVPECL、该输出具有240欧姆的偏置电阻器。 还显示了时钟基准和扇出缓冲器的原理图。