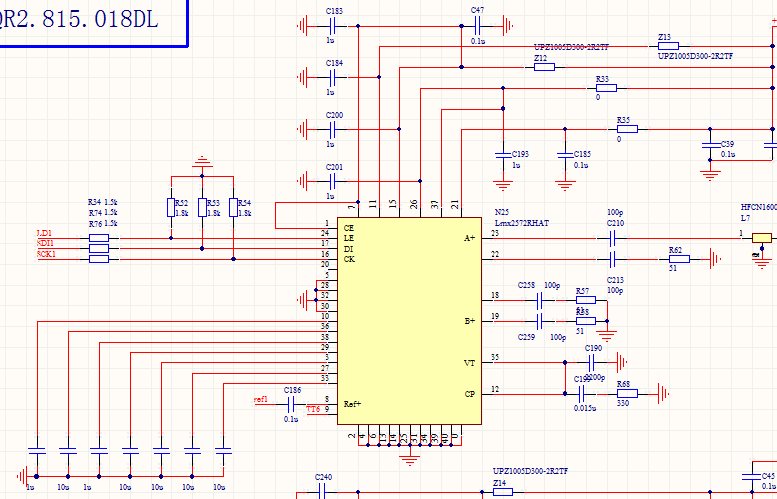

主题中讨论的其他器件: LMX2592

我们使用 LMX2572生成第1 个本地振荡 器(-5dBm 102.4MHz 参考输入、具有内部50 Ω 终端、单端输入)。 当我设置频率2757.4MHz 或(__LW_AT__2655+N*102.4)MHz,RFout 上将有一个2655MHz 的信号(__LW_AT__大约 -100dBm),它将产生一个不需要的信号;此外,参考102.4MHz,102.4*26=2662.4MHz 的谐波也将出现 在 RFout 引脚上。 如何减少不需要的信号。PCB 是6层。 我的英语很差。

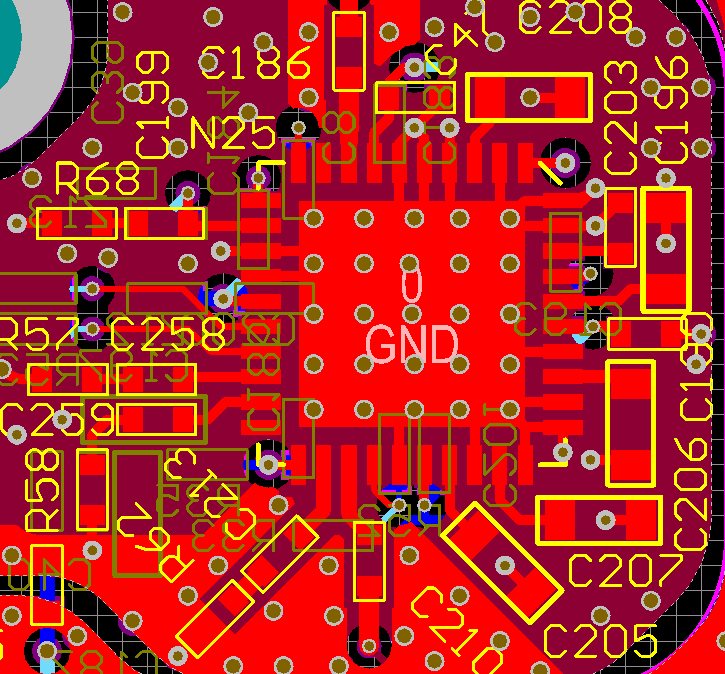

播放器

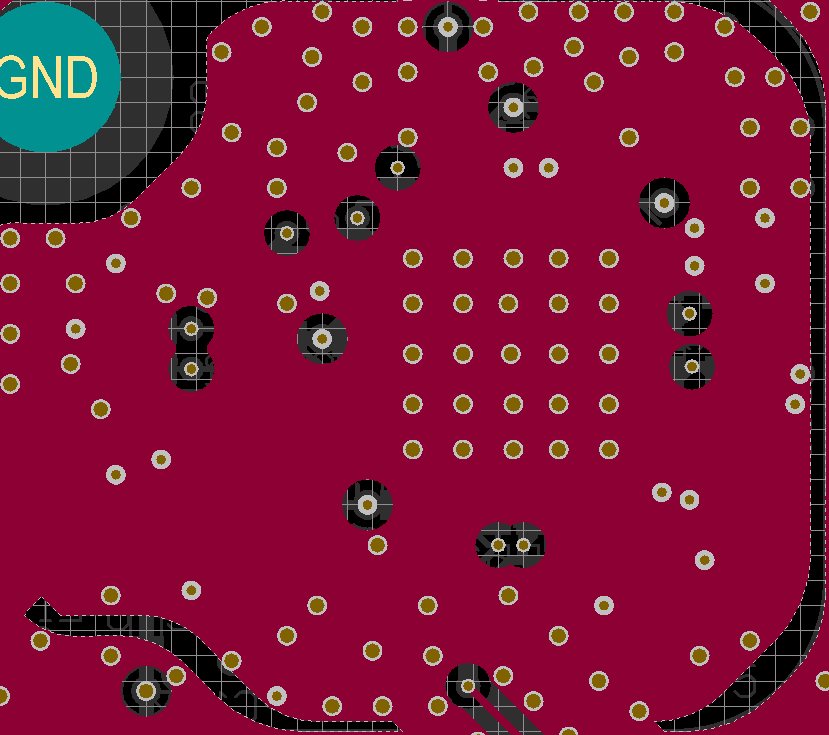

中间层1 GND

中间层2 GND SPI 控制 和 VTune

中间层3是 GND ,中间层4是 GND 和基准输入,底部是 GND 和电源