Other Parts Discussed in Thread: LMK04610, LMK04828

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04610 主题中讨论的其他器件: LMK04828

大家好、

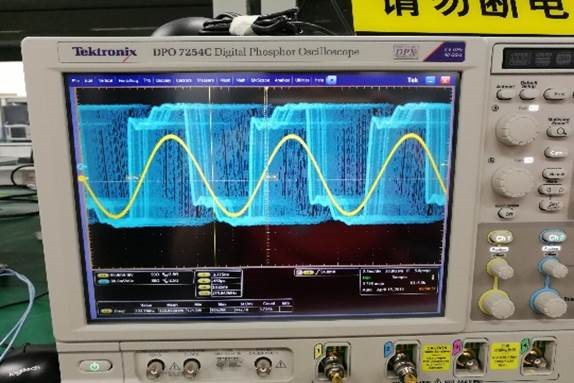

客户希望在有输入时实现快速锁定。 根据下面的频谱分析仪、当 LMK04610锁定在122.88MHz LMK04610输出时钟122.88MHz 时、REF CLK 时钟相对于 PLL1的相位仍在变化、相对稳定需要大约5秒。

1.我可以在这个应用中使用 PLL 快速锁定功能吗?

2、为什么我们需要5秒才能锁定、而 LMK04828则需要5秒

3.当我增加锁周期时、锁定时间会减少、我可以使用它吗?

4图2是我尝试实现最低相移的最佳情况、有什么方法可以改进它?

谢谢。