Other Parts Discussed in Thread: LMK03318

你好。

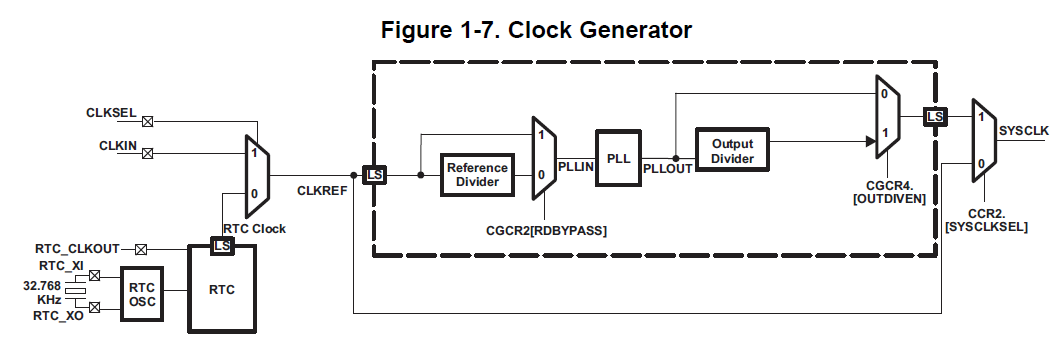

我们使用 webench 仿真来识别 LMK03318的抖动 RMS 规格。

我客户的输入方法是 LVPECL、输出方法是 CML。

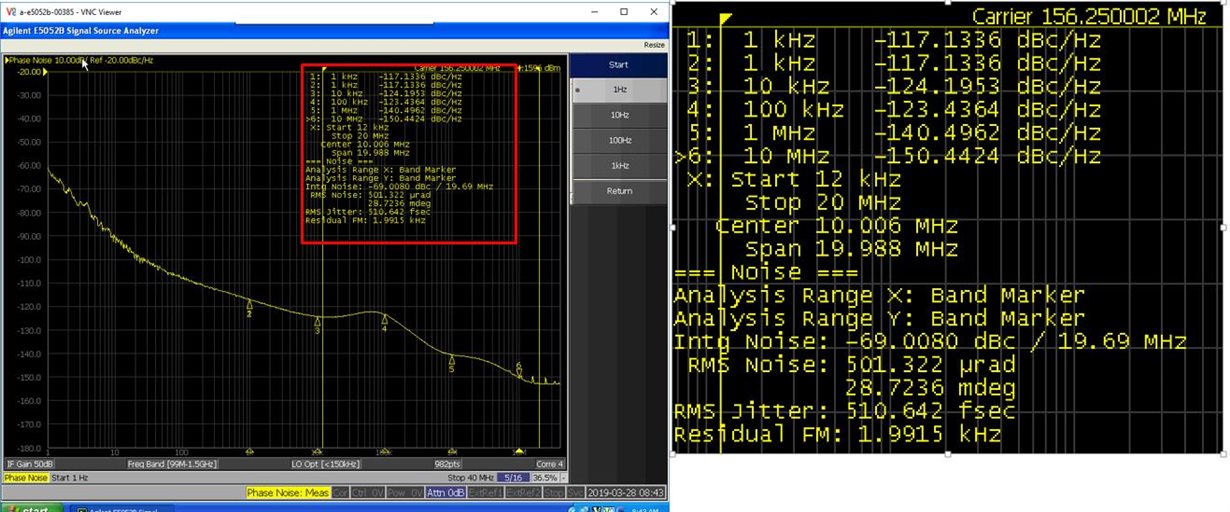

当相位噪声范围设置为12kHz 至20MHz 并且处于客户的规格范围内时、输出抖动 RMS 计算为1181fs。

此时、我认为输入 LVPECL 的抖动值最高可达510 fs。 这是否会影响输出抖动 RMS 值?

我的客户希望输出抖动 RMS 值在150fs 以内。

请检查一下。