请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04826 戴尔

戴尔

LMK04826经过设计并可进行测试。

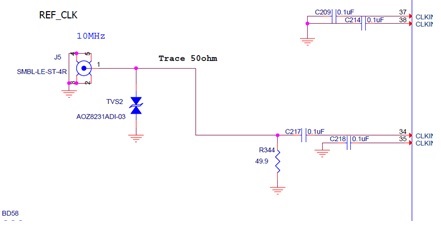

Ref_CLK = 10MHz。

10MHz 由信号发生器供电。

当10MHz 电平小于5dBm 时、PLL 锁定不起作用。

即使 R344被移除并且输入的10MHz 电平高达0dBm、它也会变成 PLL 锁定。

为什么 PLL 锁定级别不同?

是否需要50欧姆?

如何将10MHz 电平设置为-3dBm 以锁定 PLL?

谢谢你