主题中讨论的其他器件: LMX2592

您好!

请帮助。

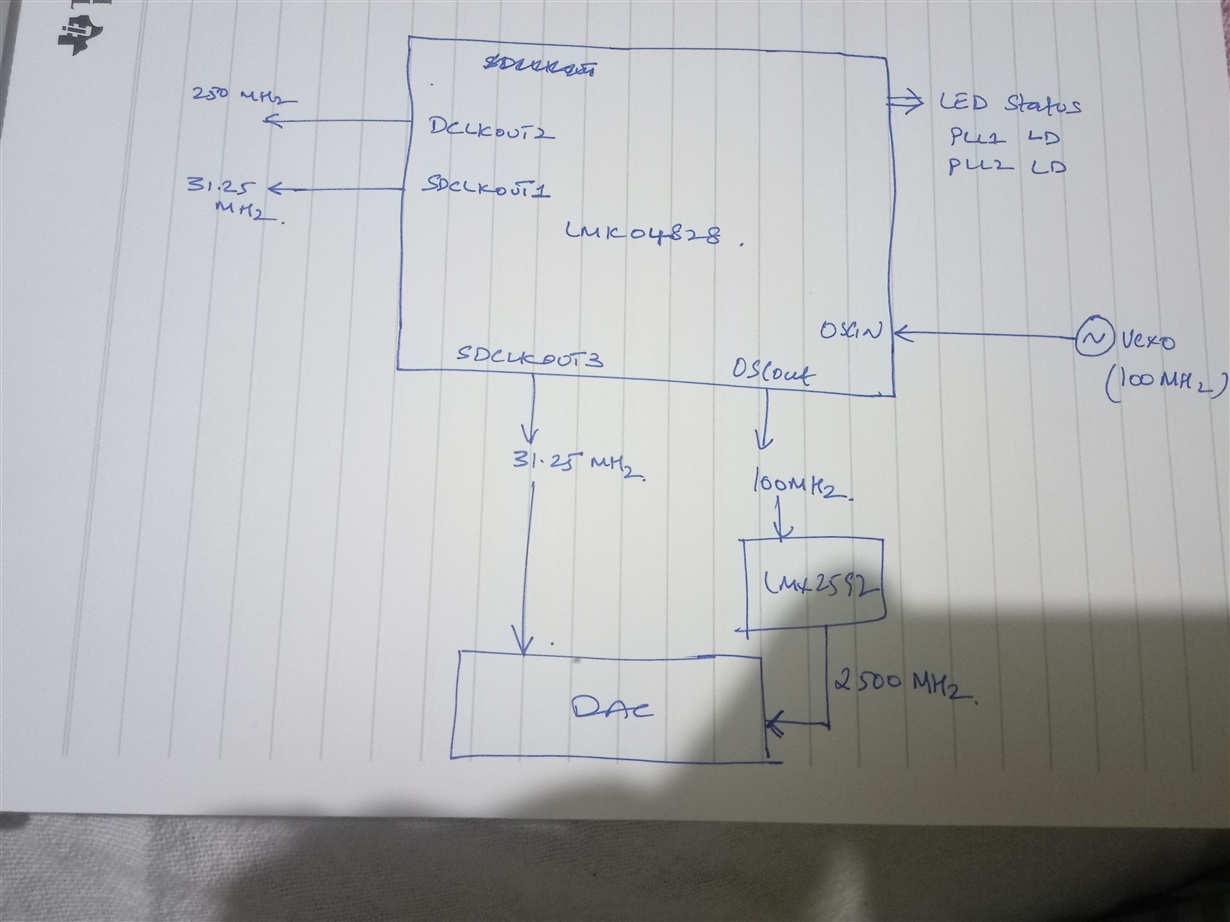

我有一个 LMK04828器件、用于为 FPGA 和 DAC 生成 sysref 和 dev clk。 DAC 的采样时钟来自 LMX2592。 LMX2592的 REFIN 源自 OSCout (100MHz)。

所示的方框图。

以下是查询。

根据上面的方框图、我只需要使用板载 VCXO (100MHz)来生成各种时钟和计时信号。 我浏览了数据表、找到了各种 clkin0、clkin1、clkin2等以及各种模式、例如手动...等等。

2、即使 我下载了 proics 以获取无法正确执行的寄存器值。

我需要监控 PLL1和 PLL2的 LED、我有板载。 当我上传内容时、我只获得 PLL2锁、但架构显示为双 PLL。 必须同时使用两个 PLL。

此处提供了使用的设置。

/*用于 DAC

* SDCLKOUT1:31.25MHz LVPECL

* DCLKOUT2:对于 JESD204内核 REFCLK 为250MHz LVPECL

* SDCLKOUT3:用于 JESD204内核 sysref 的31.25MHz LVDS

* OSCOUT:通过缓冲器连接到两个 LMX2592 OSCIN

* PLL1:100MHz pdf=10MHz

* PLL2 VCO0 2.5GHz pdf = 50MHz;n 预分频器= 2 (最小值);r=2;n=0x19 (2500/2/50=25)

*

0x000、0x80、

0x002、0、

0x003、0、

0x004、0、

0x005、0、

0x006、0、

0x00C、0、

0x00D、0、

//------ 器件时钟和 SYSREF 时钟输出控制(0x100 - 0x137)---

0x100、0x2A、

0x101、0x55、

0x103、0x00、

0x104、0x20、

0x105、0x00、

0x106、0xF2、

0x107、0x50、

0x108、0x2A、

0x109、0x55、

0x10B、0x00、

0x10C、0x20、

0x10D、0x00、

0x10E、0xF2、

0x10F、0x15、

0x110、0x38、

0x111、0x55、

0x113、0x0、

0x114、0x20、

0x115、0x0、

0x116、0xFB、

0x117、0x00、

0x118、0x38、

0x119、0x55、

0x11b、0x0、

0x11C、0x20、

0x11D、0x0、

0x11E、0xFB、

0x11F、0x00、

0x120、0x8、

0x121、0x55、

0x123、0x0、

0x124、0x0、

0x125、0x0、

0x126、0xFB、

0x127、0x0、

0x128、0x2A、

0x129、0x55、

0x12B、0x0、

0x12C、0x20、

0x12D、0x0、

0x12E、0xFB、

0x12F、0x00、

0x130、0x2A、

0x131、0x55、

0x133、0x0、

0x134、0x20、

0x135、0x0、

0x136、0xFB、

0x137、0x00、

//---------- SYSREF、SYNC 和器件配置---

0x138、0x01、

0x139、0x0、

0x13A、0x0、

0x13B、0x50、

0x13C、0x0、

0x13D、0x8、

0x13E、0x3、

0x13F、0x0、

0x140、0x1、

0x141、0x0、

0x142、0x0、

0x143、0x11、

0x144、0x0、

0x145、0x7F、

//---------- CLKIN 控制(0x146 - 0x149)----

0x146、0x18、

0x147、0x0A、

0x148、0x0B、

0x149、0x0B、

//------ RESET_Mux 和 RESET_TYPE ------------

0x14A、0x02、

//---- 0x14B - 0x152 Holdover --------

0x14B、0x32、

0x14C、0x00、

0x14D、0x00、

0x14E、0x00、

0x14F、0x7F、

0x150、0x03、

0x151、0x02、

0x152、0x00、

//---------- PLL1配置(0x153 - 0x15F)---

0x153、0x00、

0x154、0x01、

0x155、0x00、

0x156、0x01、

0x157、0x00、

0x158、0x01、

0x159、0x00、

0x15A、0x0A、

0x15B、0xD4、

0x15C、0x20、

0x15D、0x00、

0x15E、0x00、

0x15F、0x0B、

//-------- PLL2配置(0x160 - 0x16E)---

0x160、0x00、

0x161、0x02、

0x162、0x44、

0x163、0x00、

0x164、0x00、

0x165、0x19、

//编程寄存器

0x171、0xAA、

0x172、0x02、

//编程寄存器0x17C 和0x17D

0x17C、0x15、

0x17D、0x33、

0x166、0x00、

0x167、0x00、

0x168、0x19、

0x169、0x59、

0x16A、0x20、

0x16B、0x00、

0x16C、0x00、

0x16D、0x00、

0x16E、0x13、

//---- 其他寄存器

0x173、0x00、

0x182、0x00、

0x183、0x00、

//---- 读回寄存器

0x184、0、

0x185、0、

0x188、0、

//无 REAACK

//0x1FFD //预置

// SPI_LO23:16] 0

//0x1FFE

// SPI_LO15:8] 0

//0x1FFF 3.

// SPI_LO7:0] 83