您好!

我遇到的问题是 PLL1锁定到基准输入、该基准输入与当前保持时钟(或之前的基准输入)以 ppm 为单位运行。

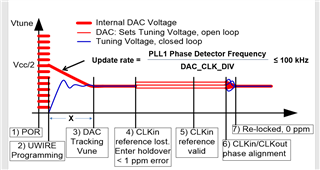

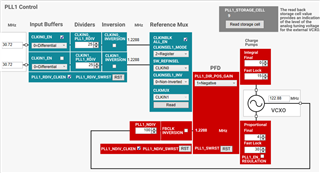

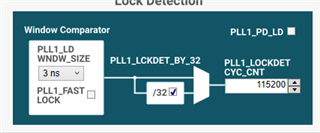

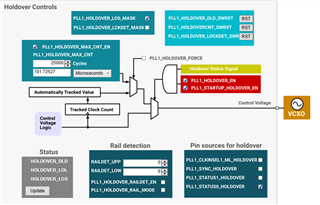

下图显示了我的输入、PLL1和保持配置、我正在使用保持功能、其中未勾选 PLL1_HOLDOW_LCKDET_MASK、以确保器件在 PLL 丢失 LO 锁定时切换到保持模式。

该器件可在测试仪触发 LOS 或 ppm 变化时轻松进入保持模式。

对于输入时钟上的任何正 ppm 变化、一旦我将 PLL1_HOLDOW_LOCKDET_SWRST 设置为从 HOLDOVER 启动复位、PLL1就能够锁定。

但是、对于测试仪的任何负 ppm 变化、PLL1很多时候都无法锁定到基准、即使 PLL1_HOLDOW_LOCKDET_SWRST 被设置后、即使输入时钟稳定(负 ppm 变化)

如下图所示、我已启用 PLL1_LOL_NORESET。

PLL1_RC_CLK_EN 标志被禁用。 您能告诉我这项功能是关于什么吗?

请查看并建议我的配置或系统中可能出现的问题。

谢谢、

Vinod