Other Parts Discussed in Thread: DAC38RF82EVM, LMK04828

主题中讨论的其他器件:DAC38RF82EVM、 DAC38RF82、

你(们)好。

我将 DAC38RF82EVM 与 TSW14J56EVM 结合使用来运行光学实验、在该实验中、我要将输出数据流(8.84736Gsps)与 DAC 同步(根据下面给出的配置进行设置)、 脉冲激光器触发器给出的外部时钟源的频率为80.028MHz:

e2e.ti.com/.../DAC38RF82_5F00_8847p36MSPS_5F00_PLL_5F00_8bitsmode_5F00_VCXO.cfg

我的想法是使用嵌套0延迟双环路、在 clkin1 (脉冲激光的80.082MHz 源)和 DAC 转换的8.84736Gsps 的数字数据之间实现固定相位关系。

根据我设置的参数 、我将使 PLL1 LD 和 PLL2 LD 变为绿色(当我从 SMA J4上拔下激光时钟时、LD 关闭)。 因此、我假设两个 PLL 都已锁定、并且所有时钟都处于同相状态。 尤其是8.84736Gsps 的 DAC 采样时钟与我的激光时钟同相。

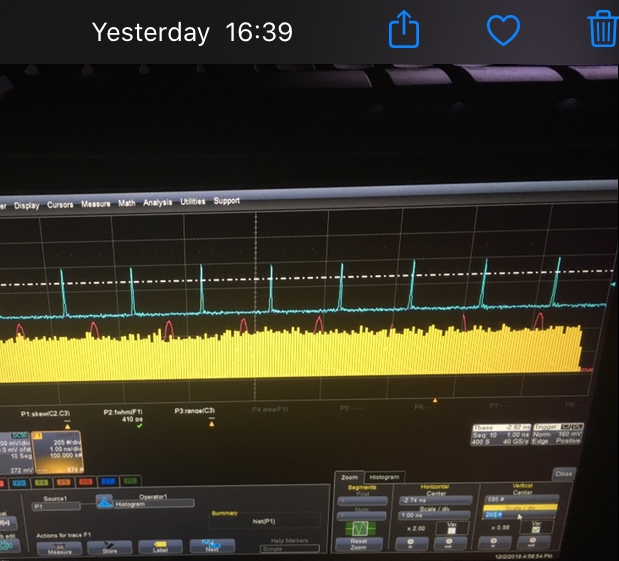

在此阶段、我生成一个波形、并将其与激光时钟一起发送到快速示波器。 我希望、如果锁定工作正常、两个脉冲会一起移动、但当我在激光时钟上触发时、我会看到生成的波形来回波动。

可以帮您解决这个问题吗? 您能建议我在 GUI 中使用哪些设置吗?

谢谢

Antonio