主题中讨论的其他器件: ADC32J25EVM

您好!

我想回顾一下我们的原理图。

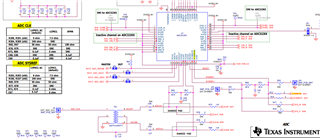

该设计包含 LMK04828、可支持 ADC32J25IRGZT 和 Xilinx FPGA。

谢谢、

Andrew

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我想回顾一下我们的原理图。

该设计包含 LMK04828、可支持 ADC32J25IRGZT 和 Xilinx FPGA。

谢谢、

Andrew

e2e.ti.com/.../FIBERSENSE_5F00_V1P07.pdf

尊敬的 Andrea:

LMK04828电路位于表18中。

问题

此致、

Andrew

您好、Andrew、

由于您尝试从器件输出3.2GHz 信号、因此 LMK04828不会为您提供足够的频率范围来获得该输出。 但是、 使用 VCO1作为内部 VCO 时、LMK04832的频率最高可达3255MHz。 在这里、您可以为160MHz 输出频率设置分频器值20、为8MHz SYSREF 输出频率设置分频器值400、为3.2GHz 输出频率设置分频器值1。 此外、您无需提供线路速率、SYSREF 频率(给出为8MHz)就足够了。

输入频率、这取决于您的应用。 驱动 LMK04828的是什么? 不同的应用具有不同的输出 频率、这些频率将成为我们系统的输入。 此外、如果您在 LMK 之前没有之前的器件说明、则可以在符合数据表规格的情况下使用任何输入频率。

告诉我您使用的输入频率后、我们可以继续操作、并按照您所述完成 TICS Pro。

谢谢、

Andrea

尊敬的 Andrew:

没错。 通常、对于符合 JESD204B 标准的时钟、FPGA 需要低频(FPGA REFCLK / CORECLK 在100MHz 以内)、并且应该能够使用 LMK04828生成低频。

对于整数时钟输出频率(SYSREF - 8MHz、 DACCLKP/N - 160MHz、 FPGACLKP/N - 160MHz 和 MGTREFCLK0P/N - 80/16/320MHz)、LMK04828内部 VCO 应是这些频率的 LCM、并且可以选择2.4GHz 的 VCO。 为了获得更好的相位噪声/抖动性能、相位检测器频率应更高。 因此、需要将现有的122.88MHz VCXO 替换为整数频率 VCXO、例如100MHz/160MHz。

随附 TICS Pro 配置文件 FYR。

e2e.ti.com/.../8272.LMK04828.tcs

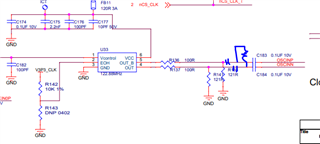

有关 LMK04828原理图、请参阅 以下反馈:

1)应遵循数据表第10.6节中的电源部分指南并基于 LMK04828EVM 用户指南。

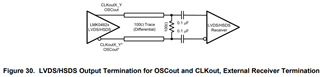

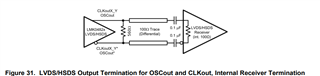

OSCin 输入需要 LVPECL 输入信号的100欧姆差分端接。 因此、可以在 C183/C184之前保持100欧姆电阻、并在 R138/R141之后插入相同的电容、以隔离共模电压变化。

SYSREFOUT 信号应来自奇数时钟输出(SDCLKoutX)。

4、如果 MGTREFCLK0P 和 FPGACLKP 的频率与 DCLKou0和 SDCLKout1相同、则应该可以、否则将这些时钟更改为不同的 DCLKout。

5.对于 LVDS 输出,如果 FPGA 具有内部100欧姆阻抗,则需要提供560欧姆,否则保持100欧姆。

CLK_TX 和 CLK_RX 的时钟频率和输出格式是什么? 如果两个频率相同、则其效果会更改为其他 DCLKout。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

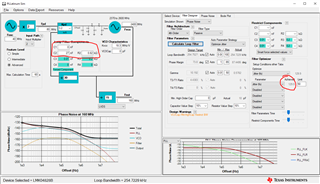

我决定输入时钟和 VCXO 使用40MHz。 决定40MHz VCXO 的原因在于成本、对于80MHz 及更高频率、成本往往会大幅增加。 在 TICS Pro 中、我能够生成2400MHz VCO。

从那里、我能够生成 ADC 和 DAC 时钟以及用于 PCIe 的100MHz。

pdf 中对配置进行了说明。

此外还随附了 TICS Pro 配置文件。

您能否查看滤波器设计"C1"(C143)、"C2"(C144)和"R2"(R121)?

e2e.ti.com/.../config_5F00_lmk04828.pdf

e2e.ti.com/.../40M.LMK04828.tcs

谢谢、

Andrew

尊敬的 Andrew:

您的频率规划看起来不错、似乎您在双 PLL 模式下使用板载基准(CLKin1)或 CLKin0 (J16)的外部基准运行 LMK04828。 所有输入基准引脚端接都很好。

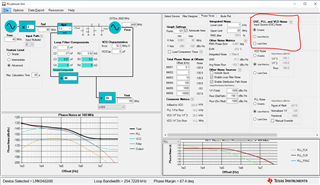

借助40MHz VCXO、您可以在路径中使用倍频器保持 PLL2相位检测器频率80MHz、这将有助于提高整体相位噪声/抖动性能。 在 PLLatinum Sim 工具中、您可以导入 VCXO 数据并进行仿真、从而获得包括 VCXO 在内的性能。

我 看不到 FPGA 的 SYSREF 输出。 通常、对于符合 JESD204B 标准的时钟、FPGA 还需要 SYSREF 输入。 请确保在 FPGA 方面、如有需要、也应包括此内容。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

首先是 TICS Pro 和 PLLatium SIM 文件。

我相信他们符合您的建议。

如果您发现任何其他问题、请告诉我。

此致、

Andrew

尊敬的 Andrew:

TICS Pro 配置文件看起来不错、但您可以启用同步功能来重置时钟分频器、使其之间的所有输出保持一致/确定性延迟。 一旦 PLL2被锁定(SYNC_PLL2_DLD -> 1)、将 SYSREF_MUX 保持在"正常同步"模式和 SYNC_DISx/SYNC_DISSYSREF -> 0、就会发生同步事件。 一旦、分频器在锁定 PLL2后复位、连续更改 SYSREF_MUX (建立 JESD 链路后、关闭 SYSREF 以避免 DCLK 上的 SYSREF 杂散)和 SYNC_DISx/SYNC_DISSYSREF -> 1。

e2e.ti.com/.../LMK04828b_5F00_updated_5F00_SYNC.tcs

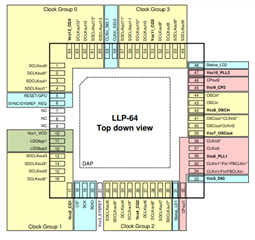

对于 噪声敏感型时钟、我建议使用来自不同时钟组的这些时钟、这样输出时钟之间的串扰将更少(就像 CLK 组1中的 ADC 时钟一样)。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

再次感谢您提供的详细反馈。 我比较了两个 TICS Pro 配置文件、以了解差异。

构建电路板时、我将使用您的配置文件。

至于时钟组、顺便说一下、ADC 时钟位于其自己的时钟组1中。

对于我们的应用、DAC 旨在生成振幅由用户控制的方波。 因此它对噪声不是很敏感。

如果您看到任何其他问题,请告诉我,环路滤波器、输入时钟电路、LVDS/LVPECL 电容器/电阻器...

如果一切正常、我们现在可以关闭此案例。

此致、

Andrew

尊敬的 Andrew:

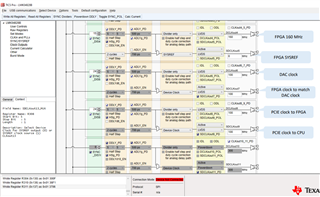

从原理图中可以看出、SDCLKout5已打开、但 TICS Pro 设置显示了 FPGA SYSREF。 您需要更新 FPGA SYSREF 输出的原理图。 与(SDCLKout9) PCIe 时钟到 CPU 类似。

关于 PLL1相位检测器频率、只需修改整数频率的 R/N 分频器即可。 之前它是十进制的0.3333333、无论如何它无关紧要、并且可在编程期间进行更改。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

抱歉。

这是更新后的原理图。

您能评论吗?

谢谢、

Andrew

尊敬的 Andrew:

对于 FPGA 时钟、我认为所有端接看起来都很好、并且配置为 LVDS 输出。

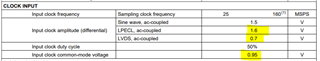

关于 ADC 时钟输入、我相信您应该关注/回顾一下 ADC 方面的内容。 这意味着、LMK04828应满足输出摆幅和共模电压(对于直流耦合)。

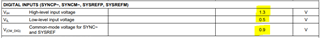

ADC32J25EVM 原理图:

现在、您已经在交流中配置了 SYSREF 并与 LVDS 耦合、但它可能不支持振幅要求。 我认为、您应该根据 EVM 原理图更改输出端接、如果是交流耦合或直流耦合 SYSREF 选项、则继续操作。

谢谢!

此致、

Ajeet Pal

您好、Ajeet、

再次感谢您的反馈。

请查看更新的原理图。

e2e.ti.com/.../FIBERSENSE_5F00_V1P16.pdf

此致、

Andrew