Thread 中讨论的其他器件:LMX2594、

|

部件 |

器件引脚 |

引脚名称 |

信号名称 |

频率 MHz |

|

LMK04208输入 |

U90-36. |

OSC_IN_P |

OSCIN_4208_CMOS

|

122.880 |

|

LMK04208输出 |

U90-4. |

CLK_OUT0_P |

SYSREF_FPGA_C_P

|

未使用 |

|

LMK04208输出 |

U90-13. |

CLK_OUT1_P |

SYSREF_RFSOC_P |

250.000 |

|

LMK04208输出 |

U90-22. |

CLK_OUT2_P |

FPGA_REFCLK_OUT_C_P |

未使用 |

|

LMK04208输出 |

U90-48 |

CLK_OUT3_P |

LMX2594A/C_SYNC |

122.880 |

|

LMK04208输出 |

U90-53. |

CLK_OUT4_P |

REFIN_2594A/C_P |

122.880 |

|

LMK04208输出 |

U90-58 |

CLK_OUT5_P |

CLK_4208_OUT5 |

10,000 |

|

LMX2594RHAT 输入 |

U102-8. |

OSCIN_P |

REFIN_2594A_C_P |

122.880 |

|

LMX2594RHAT 输出 |

U102-23. |

RF_OUT_P |

RF1_CLKO_A_P |

250.000 |

|

LMX2594RHAT 输出 |

U102-19. |

RF_OUTB_P |

RF1_CLKO_B_P |

250.000 |

|

LMX2594RHAT 输入 |

U104-8. |

OSCIN_P |

REFIN_2594C_P_P |

122.880 |

|

LMX2594RHAT 输出 |

U104-23. |

RF_OUT_P |

RF3_CLKO_A_P |

250.000 |

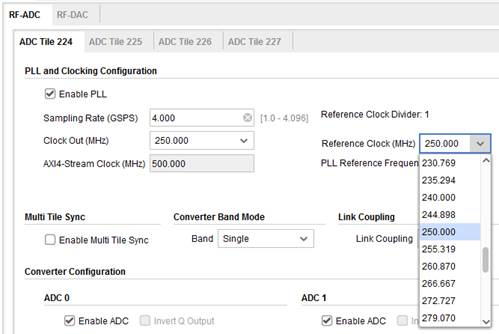

1。 此逻辑的 IP 发生器具有许多参考时钟选项、请参阅下面的示例。 该相同的基准也用于 DAC。 对于参考时钟、还有许多其他选项未显示在下图中。

2. 2. Xilinx 的 TRD 示例参考设计此板的 ADC 时钟频率为4.096GHz、使用了245.760MHz 的参考时钟。 我能够获得 WebBench 工具来找到解决方案。 如果这样做更容易、我们可以将 ADC 和 DAC 的时钟频率设置为该频率。

|

部件 |

器件引脚 |

引脚名称 |

信号名称 |

频率 MHz |

|

LMK04208输入 |

U90-36. |

OSC_IN_P |

OSCIN_4208_CMOS

|

122.880 |

|

LMK04208输出 |

U90-4. |

CLK_OUT0_P |

SYSREF_FPGA_C_P

|

未使用 |

|

LMK04208输出 |

U90-13. |

CLK_OUT1_P |

SYSREF_RFSOC_P |

250.000 |

|

LMK04208输出 |

U90-22. |

CLK_OUT2_P |

FPGA_REFCLK_OUT_C_P |

未使用 |

|

LMK04208输出 |

U90-48 |

CLK_OUT3_P |

LMX2594A/C_SYNC |

122.880 |

|

LMK04208输出 |

U90-53. |

CLK_OUT4_P |

REFIN_2594A/C_P |

122.880 |

|

LMK04208输出 |

U90-58 |

CLK_OUT5_P |

CLK_4208_OUT5 |

10,000 |

|

LMX2594RHAT 输入 |

U102-8. |

OSCIN_P |

REFIN_2594A_C_P |

122.880 |

|

LMX2594RHAT 输出 |

U102-23. |

RF_OUT_P |

RF1_CLKO_A_P |

250.000 |

|

LMX2594RHAT 输出 |

U102-19. |

RF_OUTB_P |

RF1_CLKO_B_P |

250.000 |

|

LMX2594RHAT 输入 |

U104-8. |

OSCIN_P |

REFIN_2594C_P_P |

122.880 |

|

LMX2594RHAT 输出 |

U104-23. |

RF_OUT_P |

RF3_CLKO_A_P |

250.000 |

此 逻辑的 IP 发生器具有许多参考时钟选项、请参阅下面的示例。 该相同的基准也用于 DAC。 对于参考时钟、还有许多其他选项未显示在下图中。

2. Xilinx 的 TRD 示例参考设计此板的 ADC 时钟频率为4.096GHz、使用了245.760MHz 的参考时钟。 我能够获得 WebBench 工具来找到解决方案。 如果这样做更容易、我们可以将 ADC 和 DAC 的时钟频率设置为该频率。