大家好、团队、

我们尝试使用 VCOCXO 作为双环路 PLL 的外部 VCXO 基准;但是、我们的电流设计无法锁定。

我们使用的10MHz VCOCXO 具有0-5V 的控制电压范围、从而导致+/-4Hz 偏差。 我们设计了一个放大器来获取 LMK04832的3.3V 输出、以驱动 VCOCXO 的0-5V 要求。

我们在配置或回路滤波器中是否缺少会导致 PLL 永不锁定的东西?

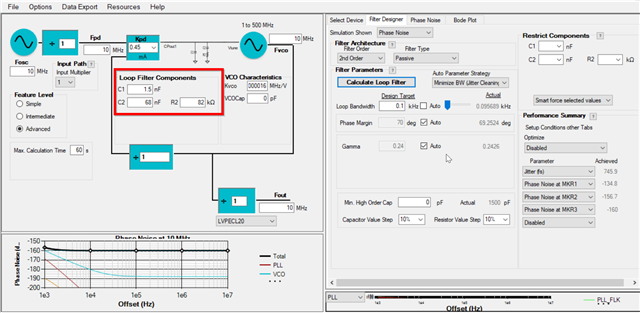

我已附加我们的 TICS 配置和环路滤波器仿真。

谢谢、

授予

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我们尝试使用 VCOCXO 作为双环路 PLL 的外部 VCXO 基准;但是、我们的电流设计无法锁定。

我们使用的10MHz VCOCXO 具有0-5V 的控制电压范围、从而导致+/-4Hz 偏差。 我们设计了一个放大器来获取 LMK04832的3.3V 输出、以驱动 VCOCXO 的0-5V 要求。

我们在配置或回路滤波器中是否缺少会导致 PLL 永不锁定的东西?

我已附加我们的 TICS 配置和环路滤波器仿真。

谢谢、

授予

尊敬的 Andrea:

感谢您的快速回复!

我们使用 VCOCXO 来减少 PLL 产生的抖动、我们使用 VCXO 完成了初始设计、但无法将抖动降低到足够低的水平。

VCOCXO 具有2Vpp 输出时钟、我们已将其连接到 PLL 的 OSCin、后者为双环路 PLL 的第二级馈送信号、并使用 CPout1驱动连接到 VCOCXO 的 ECF 引脚的放大器。 您能否进一步说明为什么这不起作用?

再次感谢你们的帮助!!

您好、Grant、

它将起作用、我误解了运算放大器 的使用方式。 为了进一步帮助您、您能告诉我以下几点吗:

1.您能否测量输入到 OCXO (Vtune)的电压? 电压是恒定值还是在变化?

2. OCXO/您能否附加您所使用的 OCXO 数据表?所需的电压是多少?

您的系统有哪些抖动要求?

LMK04832的应用是什么? 您的系统中如何使用我们的器件?

谢谢、

Andrea

尊敬的 Andrea:

以下是您请求的附加信息:

谢谢、

授予

您好、Grant、

根据您的 Vtune 值、电荷泵似乎泄漏电流、这是不可取的;但是、为了确保这是正确的、您能否向我发送一张图片、说明从同一引脚产生的信号?

作为参考、泄漏电流的原因是 Vtune 节点之后的阻抗不够高(在本例中为运算放大器的输入)。 这种较低的阻抗不会"阻断"从电荷泵流入 OCXO 的电流、这会导致环路滤波器的组件无法接收足够的电流、也不能正确为电容器充电、从而导致 PLL 块无法正常工作。 因此、要解决此问题、您可以增加电荷泵(这也会增加相位噪声)或增加 PFD 频率(从而降低相位噪声)。

此外、您尝试使用 OCXO 而不是以前使用的 VCXO 来降低多少抖动? VCXO 为您提供了多少抖动?

谢谢、

Andrea

尊敬的 Andrea:

我已根据请求连接 CPout1的输出、信号偶尔在1.5V 和0V 之间变化(每秒几次)、否则为0V。 这是在环回滤波器之前的 CPout1引脚上测得的。

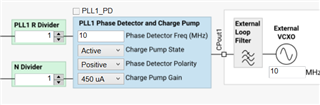

感谢您解释了泄漏电流的原因。 我们尝试将 PFD 增加到10MHz、如下所示、这导致 CPout1信号保持在1.5V、而不会出现1MHz 实现中的信号变化。 但是、我们仍然无法锁定信号。

在 VCXO 设计中、我们看到三位纳秒抖动、因此我们尝试使用 VCOCXO 将抖动降低100倍。

谢谢、

授予

您好、Grant、

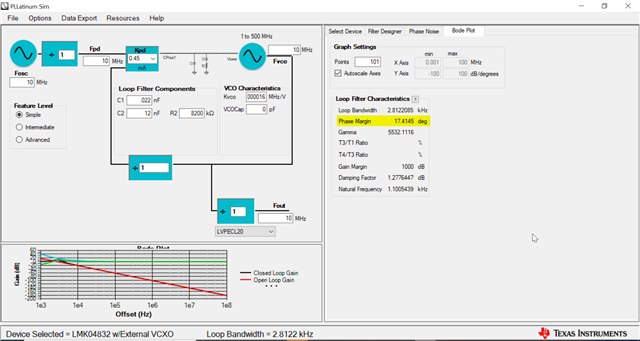

感谢您提供所有这些信息。 当您更改 PFD 时、您是否也更改了环路滤波器值? 如果您没有锁定、这就是您的 PLL 未锁定的原因。 我在 PLLatinum Sim 中使用新的 PFD 运行仿真、之前的环路滤波器拓扑为17度、这会使环路滤波器不稳定、无法锁定 PLL。

相反、我建议您的环路滤波器具有以下值:

环路滤波器取决于 PFD、环路滤波器组件、电荷泵和 Kvco;因此、 当您增大 PFD (并且保持环路滤波器不变)时、会导致相位裕度降低并使环路滤波器不稳定。

此外、如果这不起作用、我建议您考虑使用 DPLL 而不是 LMK04832、或者考虑使用性能更好的 VCXO。 它还将用作抖动清除器和时钟发生器、但不需要使用 VCXO。 根据您的应用、我推荐 使用 LMK5B33216。 它具有低抖动输出、可生成所需的输出频率。 如果该解决方案不会锁定您的 PLL、请务必告知我。

祝你好运、

Andrea